Reset Generation

Élan™SC520 Microcontroller User’s Manual 6-5

CPU reset, see the

Am486

®

DX/DX2 Microprocessor Hardware Reference Manual

, 1994

(order #17965).

Note: The CFG3–CFG0 and RSTLD7–RSTLD0 pins are latched only as a result of the

assertion of the PWRGOOD signal, and not as a result of the SYS_RST bit, AMDebug

system reset event, or watchdog timer event.

If the ICE_ON_RST bit in the Reset Configuration (RESCFG) register is set to a 1, the

AMDebug utility enters into AMDebug mode after system reset.

The states of the ÉlanSC520 microcontroller cores after system reset are shown in

Table 6-4. See the “Initialization” section at the end of each chapter for more detailed

information.

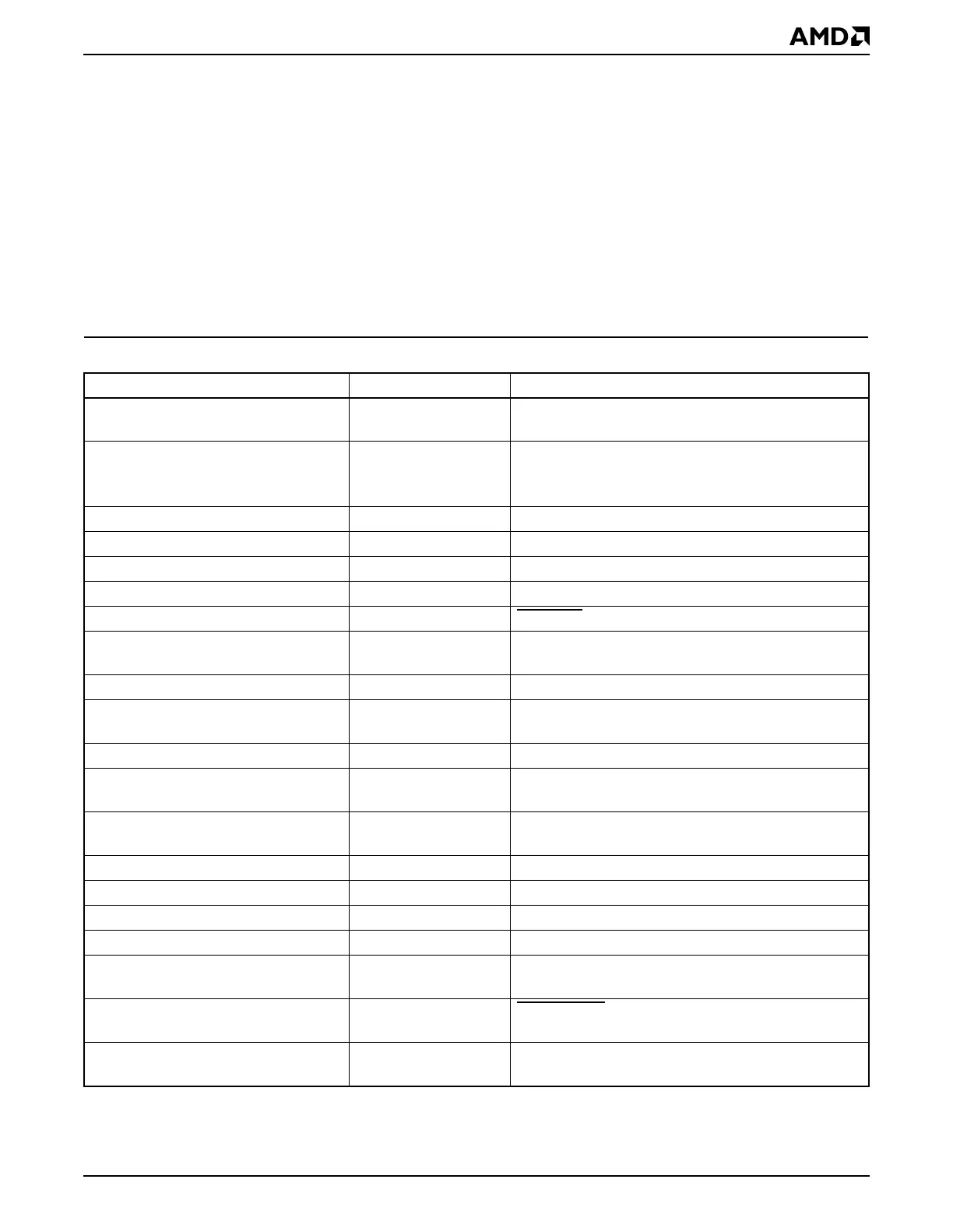

Table 6-4 States of Cores after System Reset

Core State Comment

Am5

x

86 CPU Enabled CPU clock frequency is set to 100 MHz. Internal

registers and internal cache are reset.

System arbiter Enabled Default is nonconcurrent arbitration mode. All bus

masters are disabled except the CPU as PCI and

internal Am5

x

86 CPU bus master.

PCI host bridge master controller Enabled

PCI host bridge target controller Disabled

SDRAM controller Disabled No banks are enabled.

Write buffer and read buffer Disabled

ROM controller Enabled BOOTCS

(only) is enabled at system reset

GP bus controller Enabled

External GP bus is disabled until PAR registers are

initialized.

GP-DMA controller Enabled All channels are masked off.

Programmable interrupt controller

(PIC)

Enabled

Interrupts are masked at the CPU. NMIs are

disabled.

Software timer Enabled

General-purpose (GP) timers Disabled

All GP timer registers are reset to 0. Each timer must

be programmed before it can be used.

Programmable interval timer (PIT) Disabled

Each PIT channel must be programmed before it

can be used.

Watchdog timer (WDT) Disabled

Real-time clock (RTC) Enabled

UARTs Disabled

Synchronous serial interface (SSI) Disabled Inactive until an SSI command is written.

Programmable input/output (PIO)

pins

Enabled

All PIO pins default to inputs and to their PIO

function.

JTAG test access port (TAP) Enabled

JTAG_TRST

should be asserted active Low to

ensure normal operation.

AMDebug mode Enabled If the ICE_ON_RST bit in the Reset Configuration

(RESCFG) register is set.

Loading...

Loading...