Programmable Interrupt Controller

15-6 Élan™SC520 Microcontroller User’s Manual

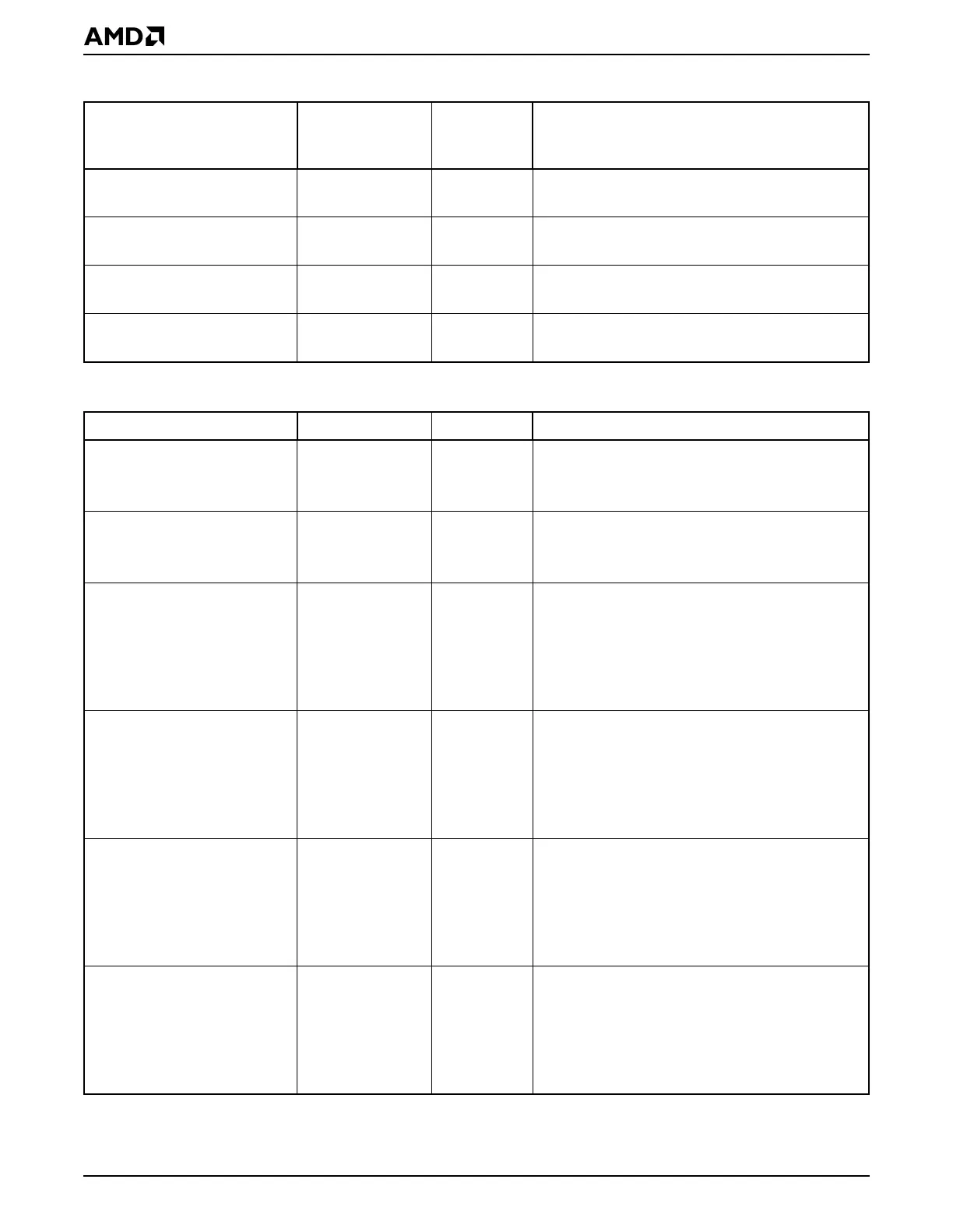

GPIRQ7 Interrupt Mapping GP7IMAP D57h GPIRQ7 interrupt mapping to any of 22 available

interrupt channels or NMI

GPIRQ8 Interrupt Mapping GP8IMAP D58h GPIRQ8 interrupt mapping to any of 22 available

interrupt channels or NMI

GPIRQ9 Interrupt Mapping GP9IMAP D59h GPIRQ9 interrupt mapping to any of 22 available

interrupt channels or NMI

GPIRQ10 Interrupt Mapping GP10IMAP D5Ah GPIRQ10 interrupt mapping to any of 22

available interrupt channels or NMI

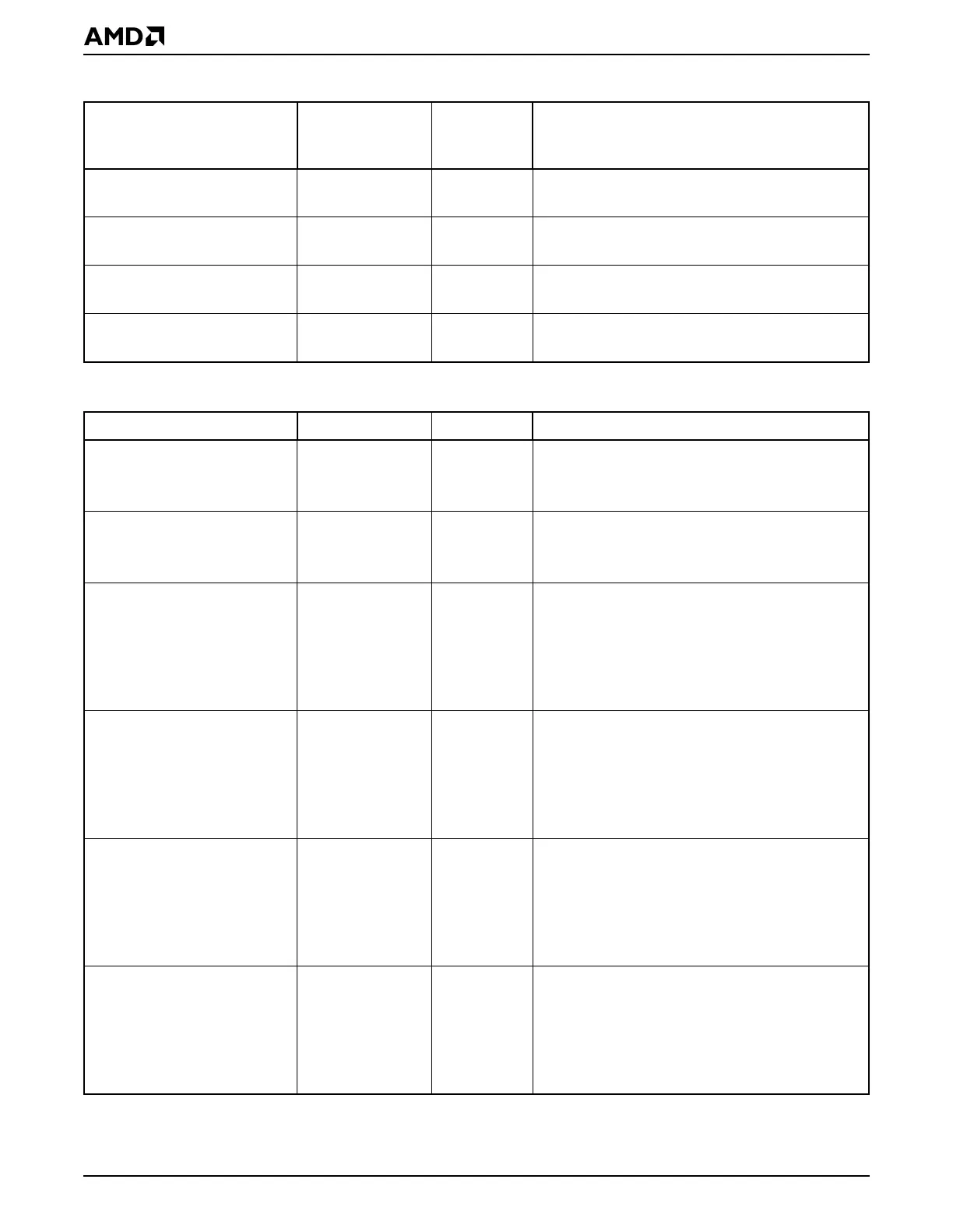

Table 15-3 Programmable Interrupt Controller Registers—Direct-Mapped

Register Mnemonic I/O Address Function

Master PIC Interrupt Request

Slave 2 PIC Interrupt Request

Slave 1 PIC Interrupt Request

MPICIR

S2PICIR

S1PICIR

0020h

0024h

00A0h

Real-time status of interrupt request assertion

Master PIC In-Service

Slave 2 PIC In-Service

Slave 1 PIC In-Service

MPICISR

S2PICISR

S1PICISR

0020h

0024h

00A0h

Interrupt request service status

Master PIC Initialization

Control Word 1 (ICW1)

Slave 2 PIC Initialization

Control Word 1 (ICW1)

Slave 1 PIC Initialization

Control Word 1 (ICW1)

MPICICW1

S2PICICW1

S1PICICW1

0020h

0024h

00A0h

Interrupt mode, address interval, cascade or

single PIC configuration, ICW4 control

Master PIC Operation Control

Word 2 (OCW2)

Slave 2 PIC Operation

Control Word 2 (OCW2)

Slave 1 PIC Operation

Control Word 2 (OCW2)

MPICOCW2

S2PICOCW2

S1PICOCW2

0020h

0024h

00A0h

Interrupt EOI, priority rotation control, EOI level

select, control to access OCW2 and OCW3

Master PIC Operation Control

Word 3 (OCW3)

Slave 2 PIC Operation

Control Word 3 (OCW3)

Slave 1 PIC Operation

Control Word 3 (OCW3)

MPICOCW3

S2PICOCW3

S1PICOCW3

0020h

0024h

00A0h

Poll command, read register command, special

mask mode

Master PIC Initialization

Control Word 2 (ICW2)

Slave 2 PIC Initialization

Control Word 2 (ICW2)

Slave 1 PIC Initialization

Control Word 2 (ICW2)

MPICICW2

S2PICICW2

S1PICICW2

0021h

0025h

00A1h

Base interrupt vector number

Table 15-2 Programmable Interrupt Controller Registers—Memory-Mapped (Continued)

Register Mnemonic

MMCR

Offset

Address Function

Loading...

Loading...