SDRAM Controller

Élan™SC520 Microcontroller User’s Manual 10-31

10.6.2.2 NOP Command

Once power is applied and the clock is stable, most SDRAM devices require a 100-µs delay

prior to applying an executable command. Therefore, boot code must guarantee that

SDRAM is not accessed immediately after reset. During this period and continuing at least

through the end of this period, the NOP command should be applied. During initialization,

the NOP command is enabled, with a binary pattern of 001b being written to the Operation

Mode Select bits. An Am5

x

86 CPU read or write cycle must be generated to the SDRAM

region to cause the generation of the specified command.

10.6.2.3 Precharge Command

Once the 100-µs delay has been satisfied with at least one NOP command having been

applied, a Precharge command should be applied to all the internal banks within a device,

thereby placing the device in the idle state. The All Banks Precharge command can be

enabled during initialization, with a binary pattern of 010b being written to the Operation

Mode Select bits. In this mode, MA10 (precharge) is held high during the precharge to

enable the All Banks Precharge. Since all banks are selected, all banks will be enabled to

interpret this command.

10.6.2.4 Auto Refresh Command

Once in the idle state, two Auto Refresh cycles must be performed. The Auto Refresh

command can be enabled during initialization, with a binary pattern of 100b being written

to the Operation Mode Select bits. The boot code must perform at least two accesses to

SDRAM when in this mode.

10.6.2.5 Mode Register Programming

Once the Auto Refresh cycles are complete, the SDRAM is ready for mode register

programming. The Load Mode Register command can be enabled during initialization with

a binary pattern of 011b being written to the OPMODE_SEL field. Since all SDRAM banks

are selected (i.e., SCS3

–SCS0 are driven active), all banks will be configured to the same

mode. The mode register is programmed to define the SDRAM devices burst length, burst

type, CAS

latency, operating mode, and write burst mode.

Of these five parameters, only the CAS

latency parameter is configured by the user via the

CAS_LAT bit in the SDRAM Timing Control (DRCTMCTL) register (MMCR offset 12h). The

programmable options for CAS

latency are 2T or 3T, where T = 15-ns clock period for a

33.333-MHz crystal. The other parameters are fixed by the ÉlanSC520 microcontroller.

Table 10-12 shows the parameters and their associated settings. All bits reflecting these

configurations are driven on the MA12–MA0 signals during a Load Mode Register

command. Since SDRAM devices require only 12 bits for the command width, MA12 is

driven Low during this cycle.

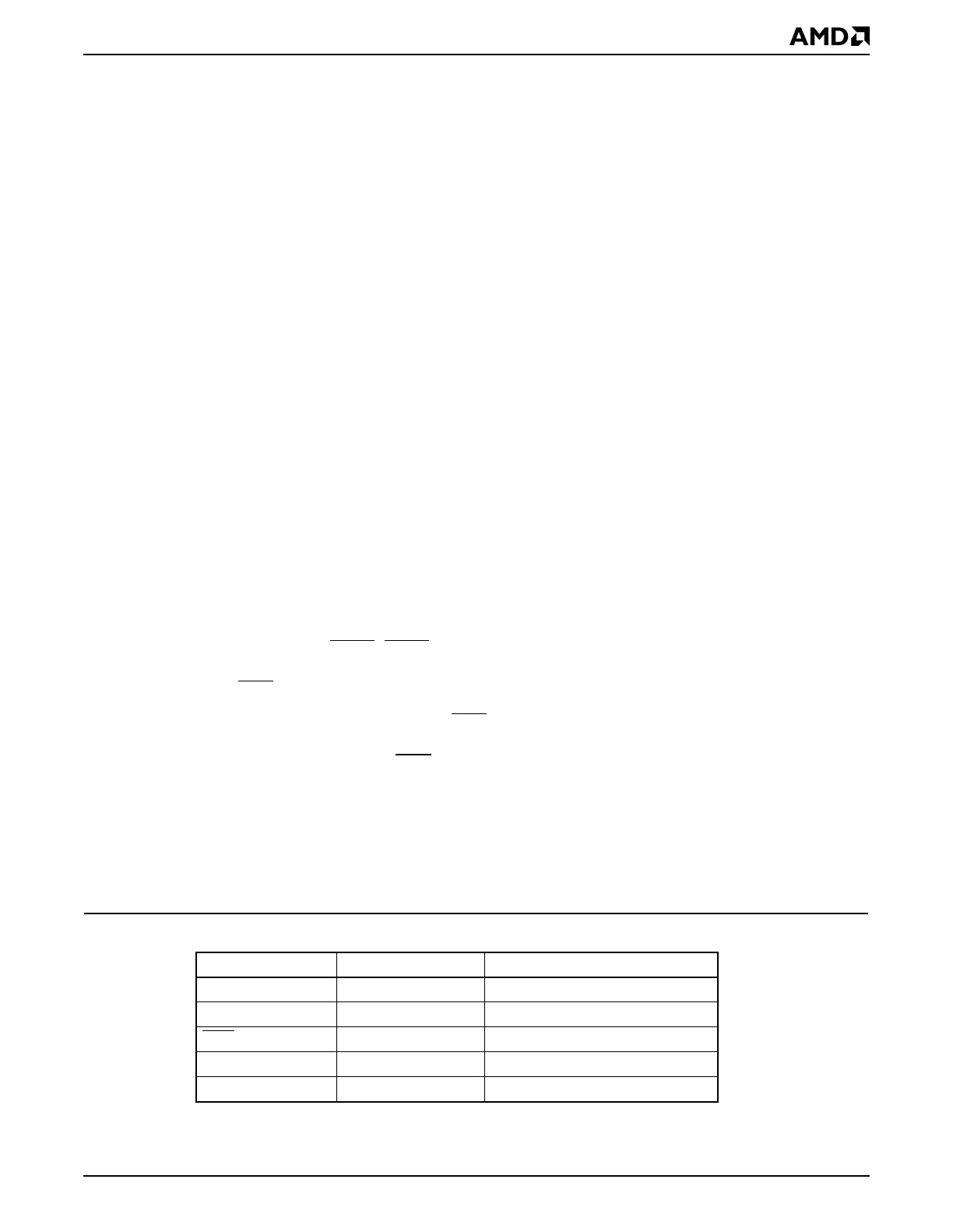

Table 10-12 Load Mode Register Settings

Parameter Setting Description

Burst length Four phases Always read burst four

Burst type Interleaved Follow non-linear burst

CAS

latency Programmable Select either 2T or 3T (see text)

Operating mode Standard operation Defined

Write burst mode Single location Single mode

Loading...

Loading...