ROM/Flash Controller

12-10 Élan™SC520 Microcontroller User’s Manual

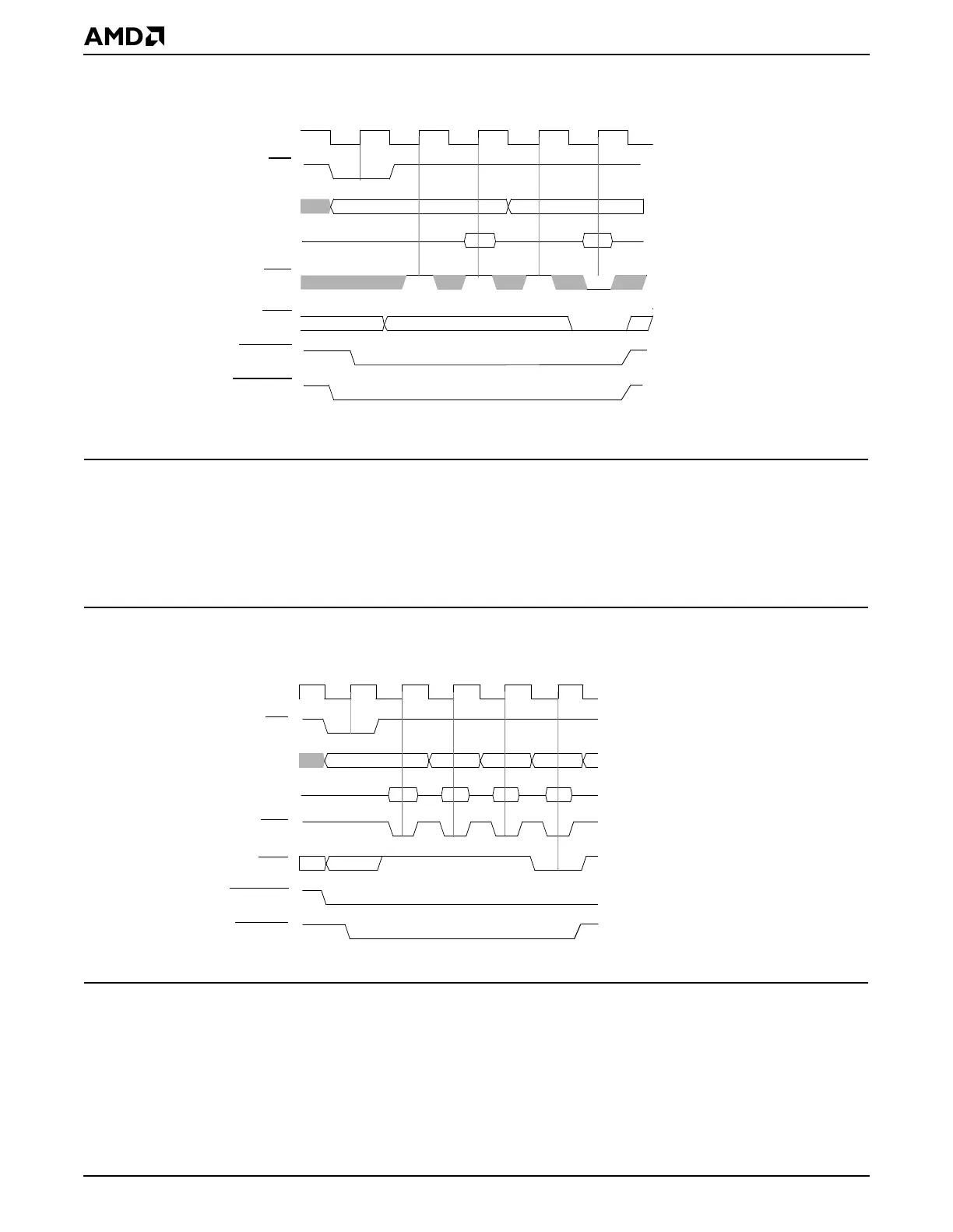

Figure 12-7 Multiple Accesses: Data Amounts Smaller than One Doubleword (2 Bytes) from

an 8-Bit ROM

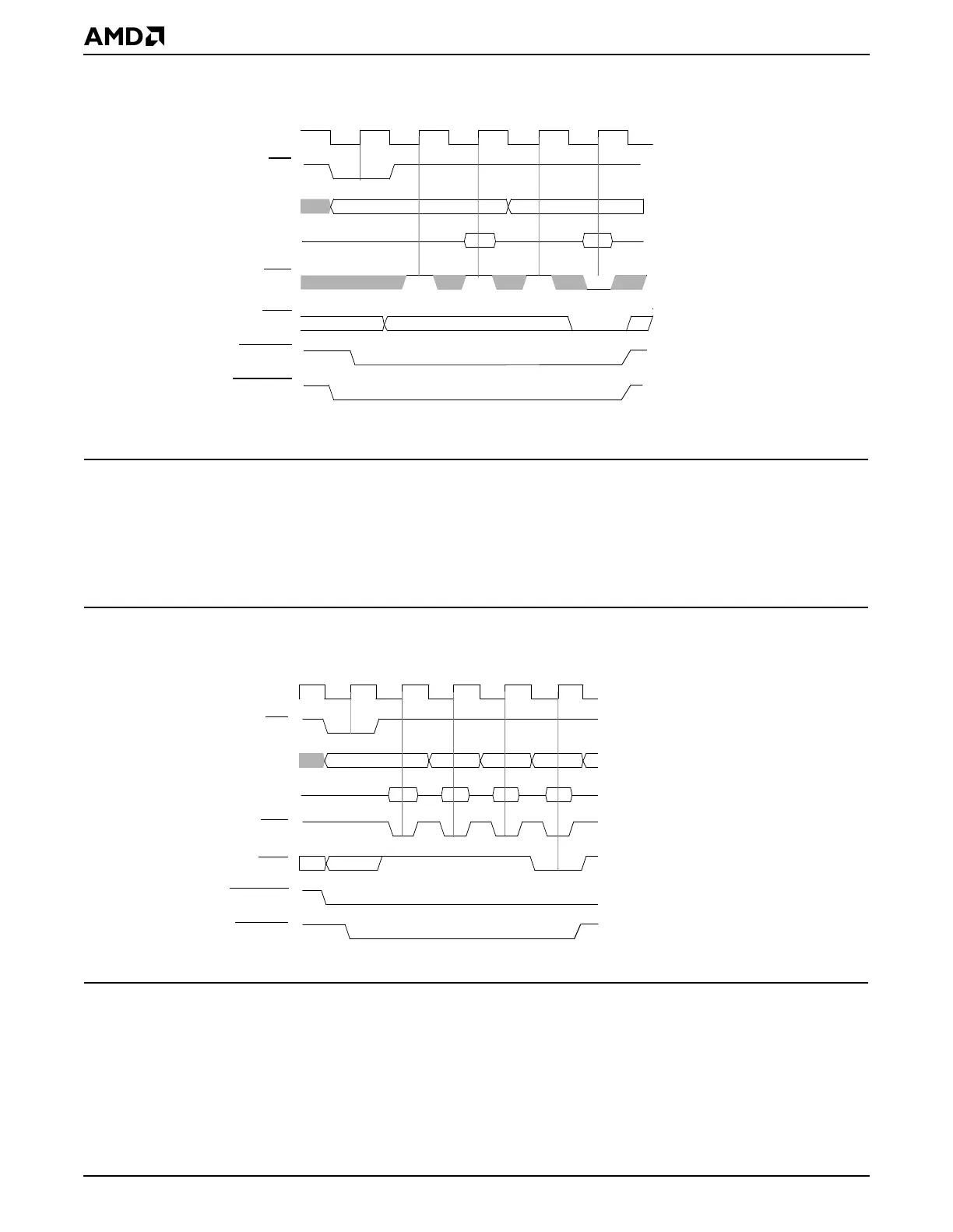

12.5.3.2 Page-Mode Read Access

The ROM controller also provides performance advantages for Am5

x

86 CPU burst

operation. Further improvement can be achieved when using page-mode ROMs. An

example is shown in Figure 12-8 for a 2-1-1-1 burst

sequence, in which the first access

requires two cycles and all subsequent accesses are performed within one cycle.

Figure 12-8 Page Access for Fetching Four Doublewords from a 32-Bit ROM

(Burst Sequence: 2-1-1-1)

During burst transfers to ROM devices with a data width smaller than 32 bits, the ROM

controller executes multiple cycles to gather the requested data. During a 32-bit request to

a 16-bit device, the ROM controller executes two 16-bit cycles. During a 32-bit request to

an 8-bit device, the ROM controller executes four 8-bit cycles. A 32-bit request to a 16-bit

ROM device is shown in Figure 12-9.

ADR+0

0

ADR+1

1

CPU clock

ads

GPA25–GPA0

GPD7–GPD0, or

brdy

blast

ROMRD

BOOTCS

Notes:

An 8-bit ROM is attached to the 16-bit GP bus.

MD7–MD0

start cycle

- - - C - - - 8 - - - 4 - - - 0

CPU clock

ads

GPA25–GPA0

MD31–MD0

brdy

blast

BOOTCS

ROMRD

Loading...

Loading...