UART Serial Ports

21-4 Élan™SC520 Microcontroller User’s Manual

UART 2 Interrupt Mapping UART2MAP D29h UART 2 interrupt mapping

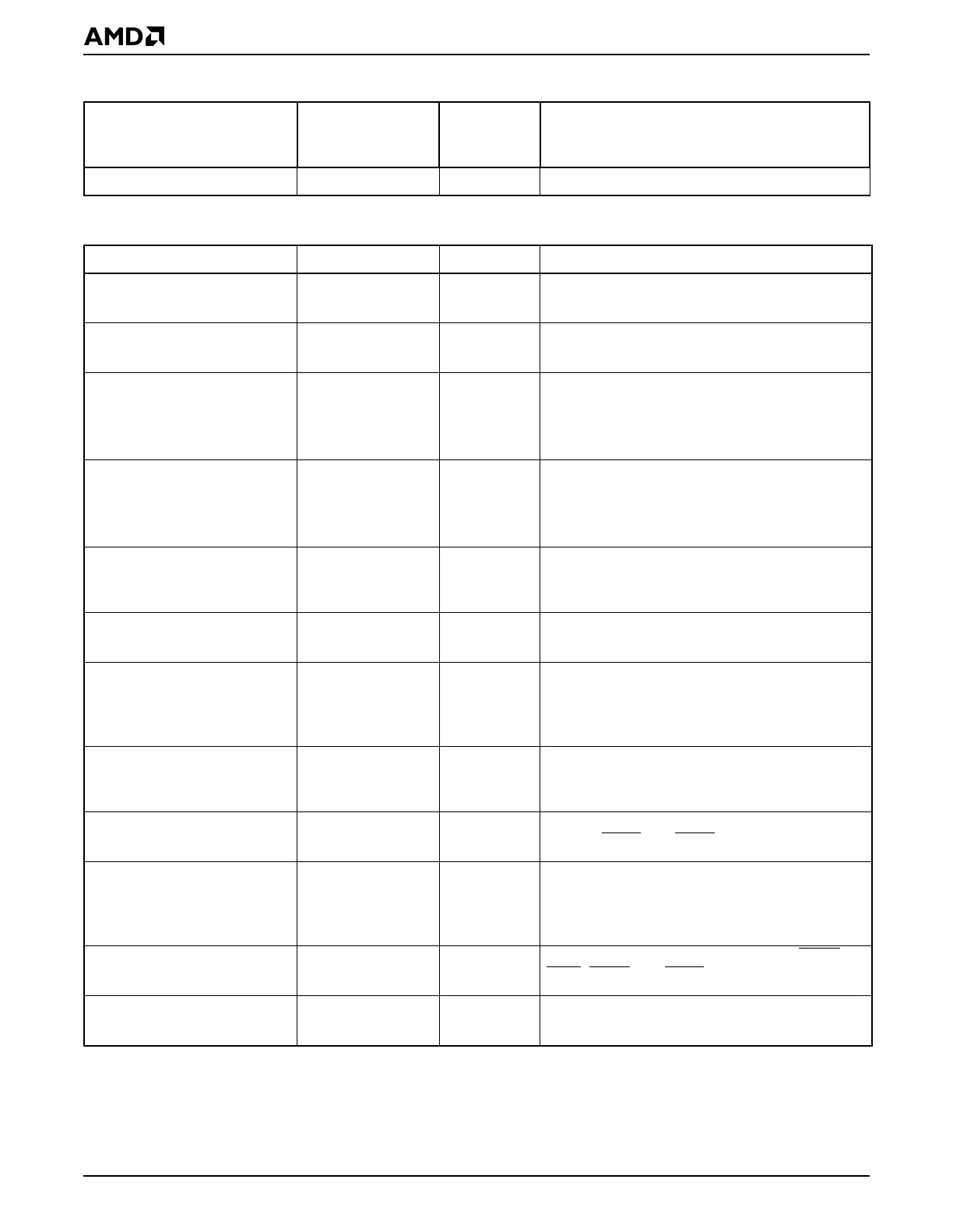

Table 21-4 UART Registers—Direct-Mapped

Register Mnemonic I/O Address Function

UART 1 Transmit Holding

UART 2 Transmit Holding

UART1THR

UART2THR

02F8h

03F8h

Byte to be transmitted

UART 1 Receive Buffer

UART 2 Receive Buffer

UART1RBR

UART2RBR

02F8h

03F8h

Received byte

UART 1 Baud Clock Divisor

Latch LSB

UART 2 Baud Clock Divisor

Latch LSB

UART1BCDL

UART2BCDL

02F8h

03F8h

Least significant byte of a 16-bit baud-rate clock

divisor used to generate the 16x baud clock

UART 1 Baud Clock Divisor

Latch MSB

UART 2 Baud Clock Divisor

Latch MSB

UART1BCDH

UART2BCDH

02F9h

03F9h

Most significant byte of a 16-bit baud-rate clock

divisor used to generate the 16x baud clock

UART 1 Interrupt Enable

UART 2 Interrupt Enable

UART1INTENB

UART2INTENB

02F9h

03F9h

Interrupt enables: modem status, receiver line

status, transmit holding empty, received data

available, and time-out

UART 1 Interrupt ID

UART 2 Interrupt ID

UART1INTID

UART2INTID

02FAh

03FAh

FIFO mode indication, interrupt identification,

interrupt pending status

UART 1 FIFO Control

UART 2 FIFO Control

UART1FCR

UART2FCR

02FAh

03FAh

Trigger level for received data available

interrupt, DMA mode, transmitter FIFO and

receiver FIFO clear, FIFO enable for 16550-

compatible mode

UART 1 Line Control

UART 2 Line Control

UART1LCR

UART2LCR

02FBh

03FBh

Divisor latch access (DLAB), break, stick parity,

parity, asynchronous data parity, stop, transmit/

receive word length

UART 1 Modem Control

UART 2 Modem Control

UART1MCR

UART2MCR

02FCh

03FCh

Loopback diagnostic mode, UARTx interrupt

enable, RTSx

and DTRx control

UART 1 Line Status

UART 2 Line Status

UART1LSR

UART2LSR

02FDh

03FDh

FIFO error, transmitter empty indicator,

Transmitter Holding register or transmit FIFO

empty, break indicator, framing error, parity

error, overrun error, data ready

UART 1 Modem Status

UART 2 Modem Status

UART1MSR

UART2MSR

02FEh

033FEh

Real-time and latched status bits for DCDx

,

RINx

, DSRx and CTSx

UART 1 Scratch Pad

UART 2 Scratch Pad

UART1SCRATCH

UART2SCRATCH

02FFh

03FFh

Temporary data storage

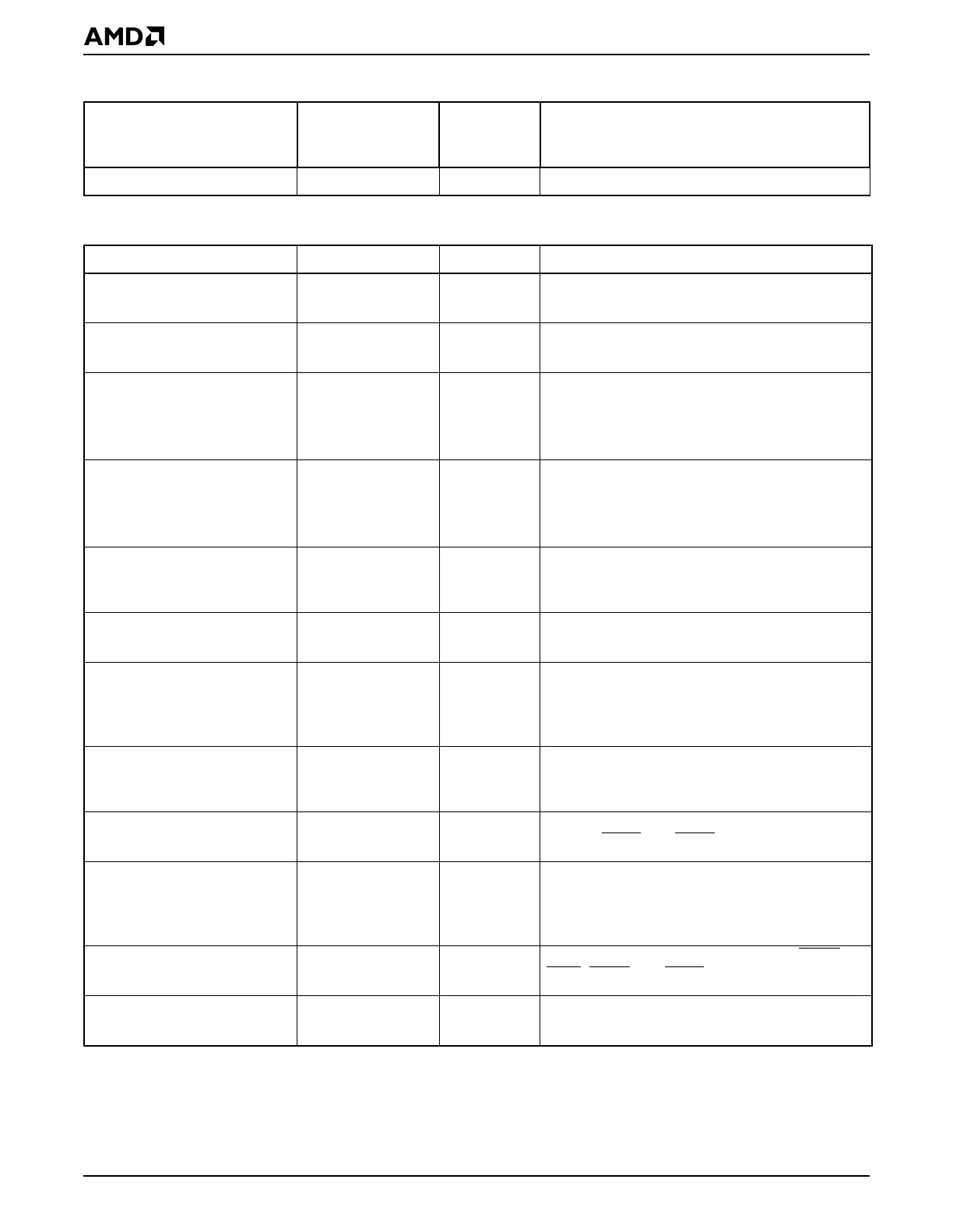

Table 21-3 UART Registers—Memory-Mapped (Continued)

Register Mnemonic

MMCR

Offset

Address Function

Loading...

Loading...