PCI Bus Host Bridge

9-26 Élan™SC520 Microcontroller User’s Manual

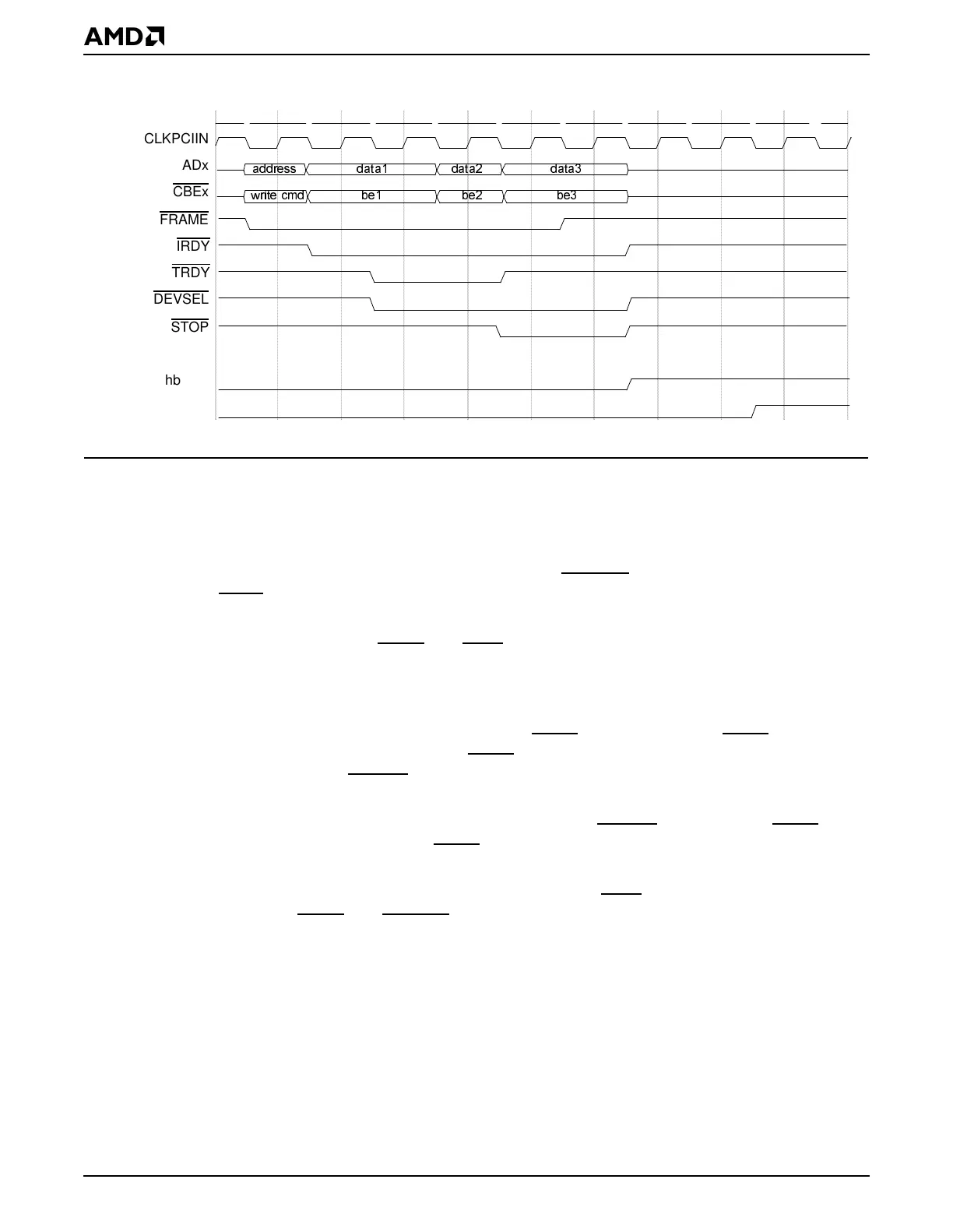

Figure 9-16 PCI Host Bridge Target Disconnect

The following sequence annotates the PCI host bridge target disconnect shown in

Figure 9-16.

■ Clock #1: An external PCI bus master initiates a write transaction to ÉlanSC520

microcontroller SDRAM.

■ Clock #3: The PCI host bridge always asserts DEVSEL with medium timing and asserts

TRDY

, signaling it is ready to accept data (provide data for external PCI bus master

reads).

■ Clocks #4–#5: Both TRDY and IRDY are sampled asserted, signaling a valid data

phase. External master write data will be accepted by the PCI host bridge (or the external

master will read data for external PCI bus master read cycles).

■ Clock #4: The PCI host bridge write FIFO is full (or the target read FIFO is empty for

external PCI bus master read cycles), so TRDY

is deasserted and STOP is asserted,

signaling a disconnect. Because TDRY

is deasserted, Clock #4 is the last valid data

phase. Note that FRAME

is still asserted, signaling that the external PCI bus master is

requesting to burst more data.

■ Clock #6: The external PCI bus master deasserts FRAME in response to STOP being

sampled asserted. Because TRDY

is deasserted, this is not a valid data phase and no

data will be transferred.

■ Clock #7: The external PCI bus master deasserts IRDY and the PCI host bridge

deasserts STOP

and DEVSEL, ending the PCI bus transaction. The host bridge has

synchronized the first PCI bus data phase (Clock #4) and requests access to the SDRAM

controller.

■ Clock #9: The CPU bus is granted to the PCI host bridge, and the PCI bus data can be

written to SDRAM. The x5_gnt signal may be delayed if the Am5

x

86 CPU or GP-DMA

controller is accessing SDRAM.

1 2 3 4 5 6 7 8 9 10

DGGUHVV GDWD GDWD GDWD

ZULWHFPG EH EH EH

CLKPCIIN

ADx

CBEx

FRAME

IRDY

TRDY

DEVSEL

STOP

hb_req

hb_gnt

Loading...

Loading...