SDRAM Controller

10-22 Élan™SC520 Microcontroller User’s Manual

10.5.6.5 Minimum RAS (T

RAS

)

The minimum RAS parameter of an SDRAM device refers to the minimum period of time

that a row must remain open. This is the period of time between an Active command and

a Precharge command to the

same

internal bank. This parameter is referred to as T

RAS

.

Since the ÉlanSC520 microcontroller performs single write cycles, the minimum T

RAS

occurs during write cycles. T

RAS

is a function of T

RCD

. This parameter is calculated as:

T

RAS

= T

RCD

(configuration setting in number of clocks) + 2T (where T refers to a 15-ns

clock period for a 33.333-MHz crystal).

A minimum T

RAS

of 5T is enforced when a T

RCD

of 2T is specified.

10.5.7 Bus Cycles

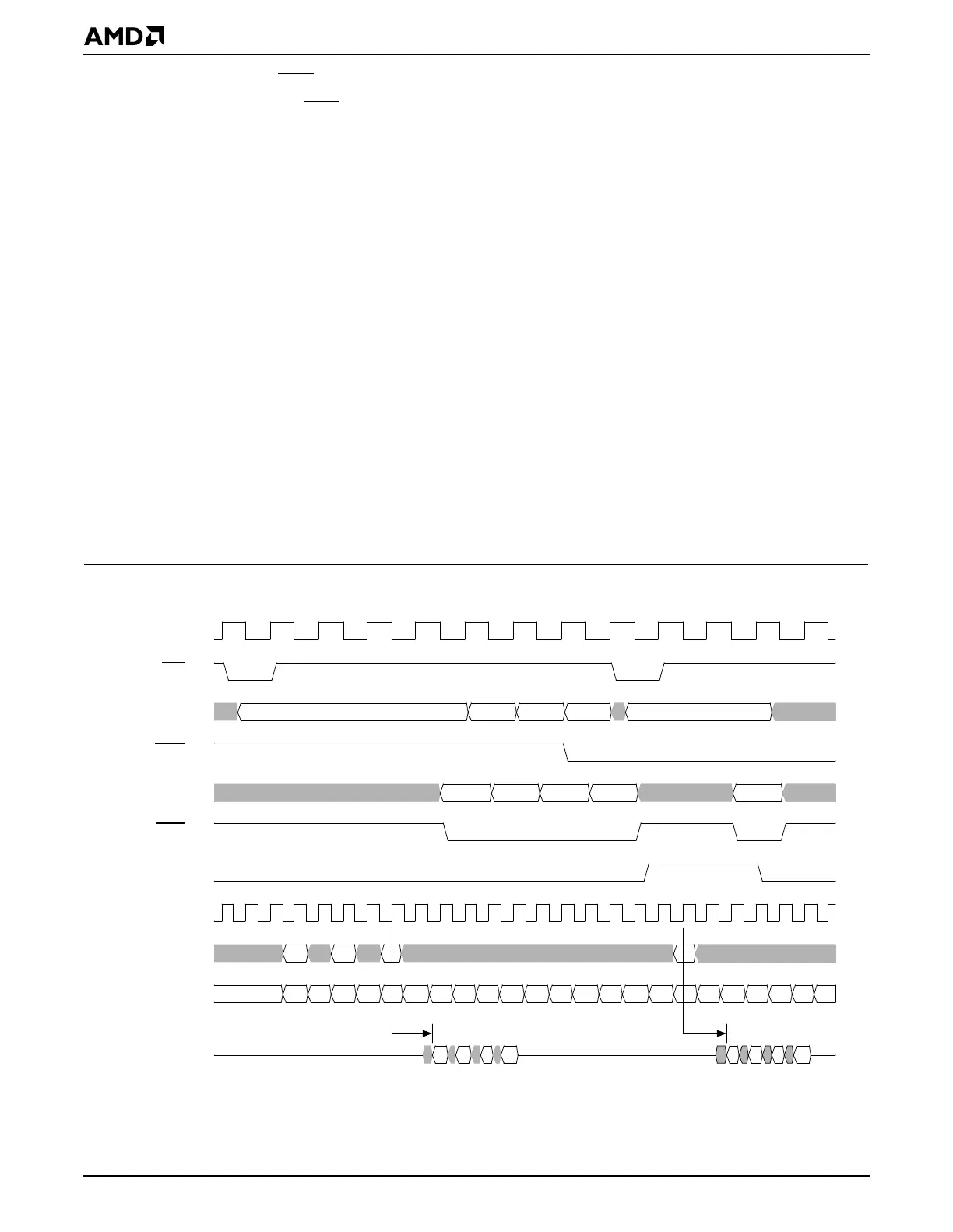

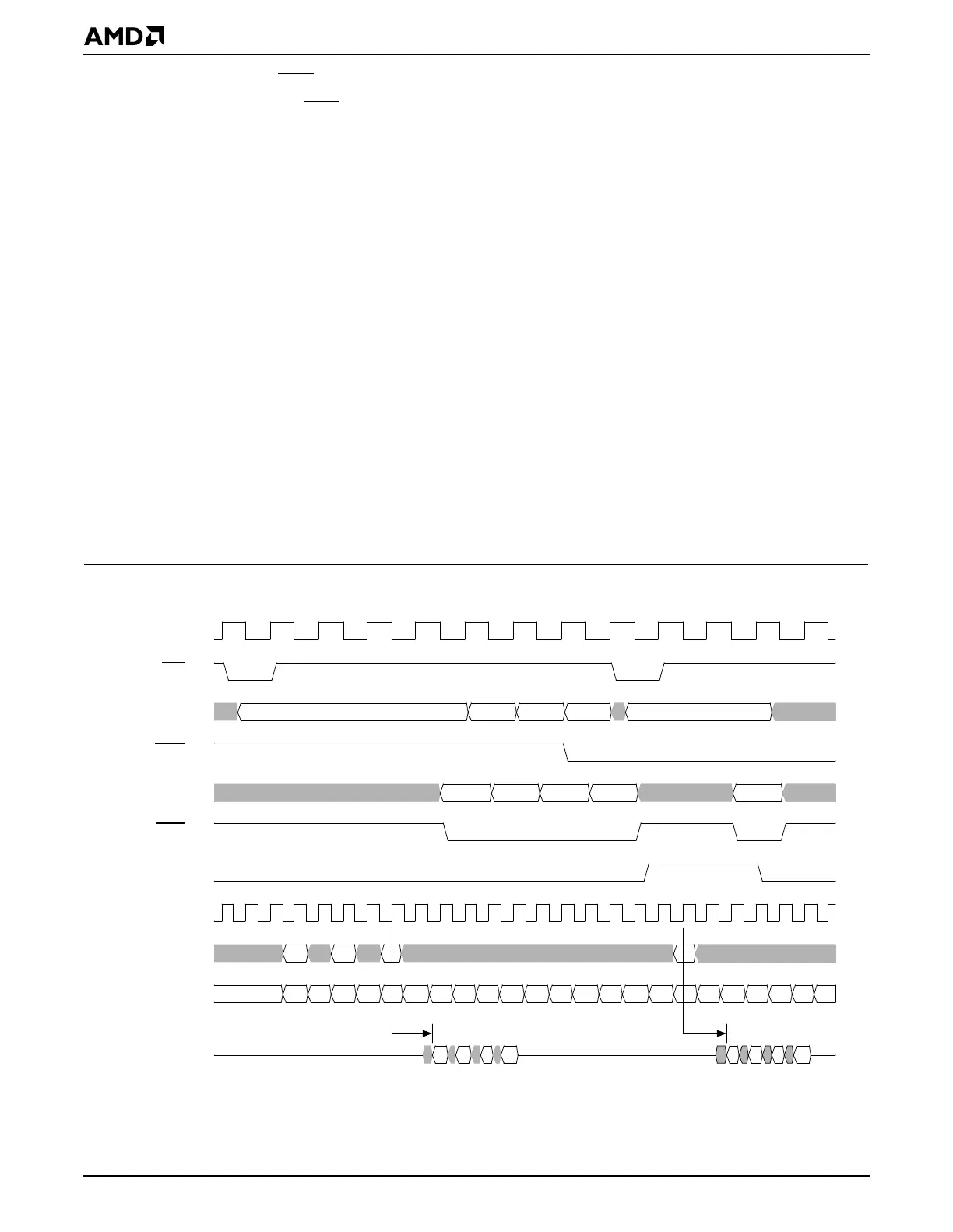

10.5.7.1 SDRAM Burst Read Cycle

The ÉlanSC520 microcontroller always bursts up to four doublewords on a read as shown

in Figure 10-7. The burst read to the SDRAM could occur due to any of the following

reasons:

■ Am5

x

86 CPU read

■ Read buffer’s read-ahead prefetch

■ ÉlanSC520 microcontroller responding to PCI burst cycle as a target

■ GP-DMA

Figure 10-7 SDRAM Burst Read Cycle (Read-Ahead Feature Disabled) (Page Miss/Page Hit)

Notes:

This timing diagram does not account for resynchronization of SDRAM signals with CLKMEMIN.

CAS latency = 2 CAS latency = 2

Rd

048C

abcd

Act

ab

c

Row

10

Rd

e

e

Col

Col

Bnk

Pre

clk_cpu

x5_abus

blast

x5_data_in

pghit

clk_mem

MA12–MA0,

Command

MD31–MD0

d

ads

brdy

BA1–BA0

Loading...

Loading...