Programmable Interrupt Controller

15-4 Élan™SC520 Microcontroller User’s Manual

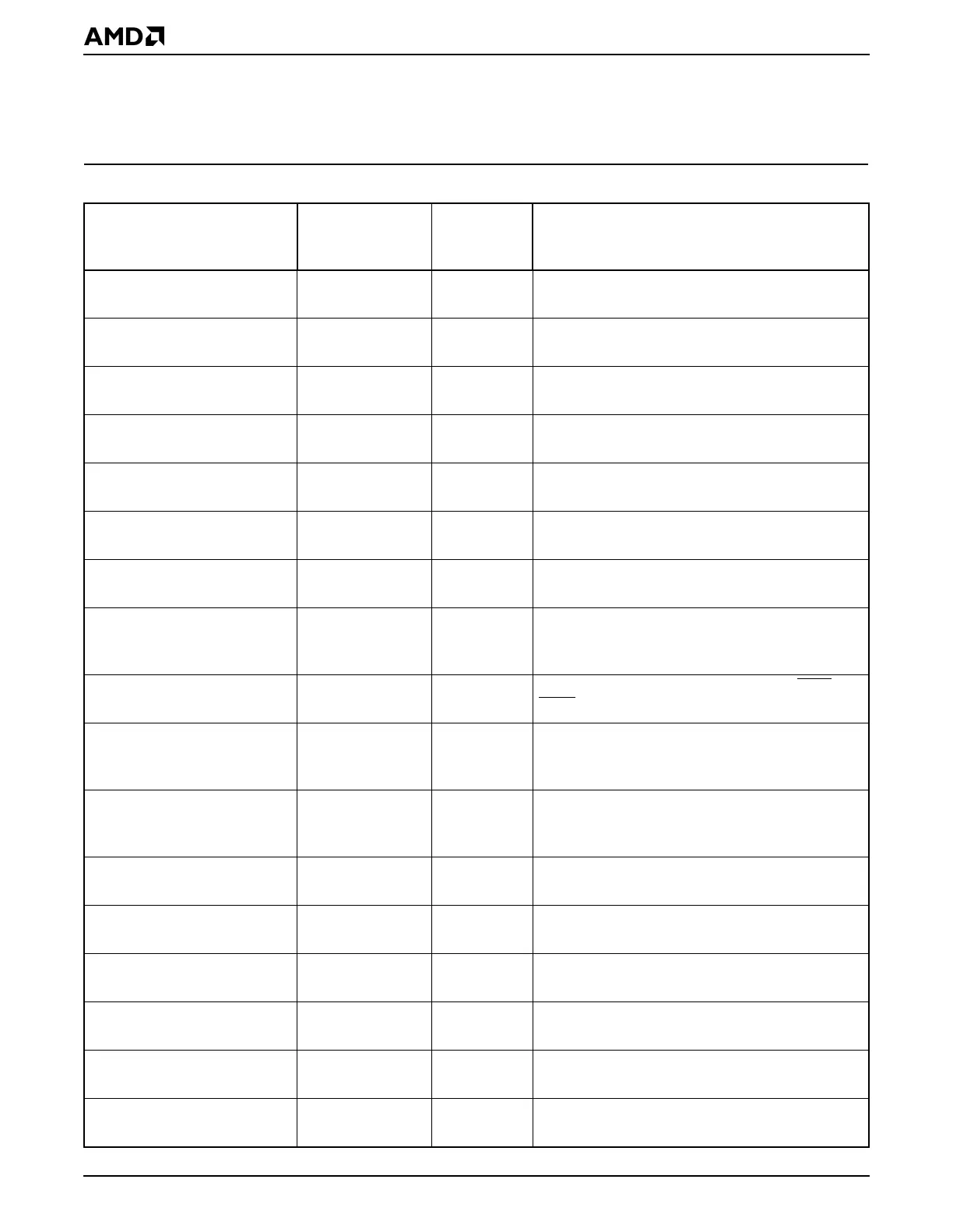

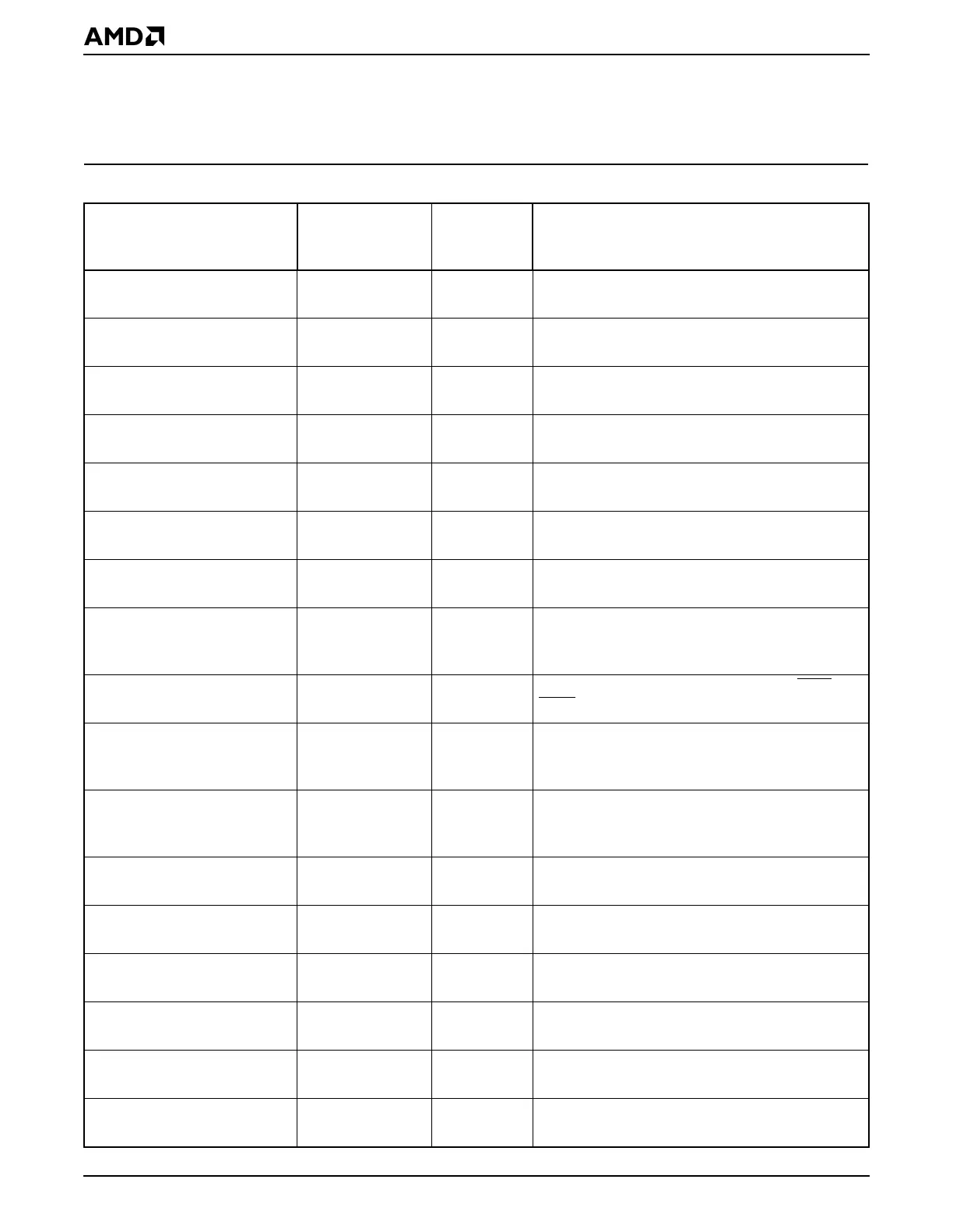

15.4 REGISTERS

The programmable interrupt controller (PIC) is controlled by the registers listed in Table 15-2

and Table 15-3.

Table 15-2 Programmable Interrupt Controller Registers—Memory-Mapped

Register Mnemonic

MMCR

Offset

Address Function

PIO15–PIO0 Pin Function

Select

PIOPFS15_0 C20h PIO or interface function select: GPIRQ10–

GPIRQ8

PIO31–PIO16 Pin Function

Select

PIOPFS31_16 C22h PIO or interface function select: GPIRQ7–

GPIRQ0

Interrupt Control PICICR D00h Global interrupt mode enables, global NMI

enable, NMI completion control

Master PIC Interrupt Mode MPICMODE D02h Edge- or level-sensitive interrupt mode select

per channel

Slave 1 PIC Interrupt Mode SL1PICMODE D03h Edge- or level-sensitive interrupt mode select

per channel

Slave 2 PIC Interrupt Mode SL2PICMODE D04h Edge- or level-sensitive interrupt mode select

per channel

Software Interrupt 16–1

Control

SWINT16_1 D08h Software interrupt generation control (priority

levels 1–16)

Software Interrupt 22–17/NMI

Control

SWINT22_17 D0Ah Software interrupt generation control (priority

level 17–22), software NMI generation to the

CPU

Interrupt Pin Polarity INTPINPOL D10h Polarity of external interrupt sources (INTA

–

INTD

and GPIRQ10–GPIRQ0)

PCI Host Bridge Interrupt

Mapping

PCIHOSTMAP D14h System arbiter and PCI Host Bridge interrupt

mapping to any of 22 available interrupt

channels or NMI, PCI NMI enable control

ECC Interrupt Mapping ECCMAP D18h ECC interrupt mapping to any of 22 available

interrupt channels or NMI, ECC NMI enable

control

GP Timer 0 Interrupt Mapping GPTMR0MAP D1Ah GP Timer 0 interrupt mapping to any of 22

available interrupt channels or NMI

GP Timer 1 Interrupt Mapping GPTMR1MAP D1Bh GP Timer 1 interrupt mapping to any of 22

available interrupt channels or NMI

GP Timer 2 Interrupt Mapping GPTMR2MAP D1Ch GP Timer 2 interrupt mapping to any of 22

available interrupt channels or NMI

PIT 0 Interrupt Mapping PIT0MAP D20h PIT 0 interrupt mapping to any of 22 available

interrupt channels or NMI

PIT 1 Interrupt Mapping PIT1MAP D21h PIT 1 interrupt mapping to any of 22 available

interrupt channels or NMI

PIT 2 Interrupt Mapping PIT2MAP D22h PIT interrupt mapping to any of 22 available

interrupt channels or NMI

Loading...

Loading...