System Test and Debugging

24-2 Élan™SC520 Microcontroller User’s Manual

24.2.1 Loading

When a logic analyzer is connected to the ÉlanSC520 microcontroller pins, it presents an

additional load that must be taken into consideration on critical buses, such as the SDRAM

interface. Extreme care must be taken when connecting to either the SDRAM clock or the

PCI bus clock. When external clock drivers are used on the system circuit board, it may be

best to connect to the output of a lightly loaded or unused clock driver.

24.3 REGISTERS

Table 24-2 lists the memory-mapped registers that are used to control the system-level

debugging features.

Table 24-1 System Test and Debugging Signals Shared with Other Interfaces

Default Signal Alternate Function Control Bit Register

CF_ROM_GPCS

WBMSTR0 WB_TST_ENB SDRAM Control (DRCCTL) register

(MMCR offset 10h)

DATASTRB WBMSTR1

CF_DRAM

WBMSTR2

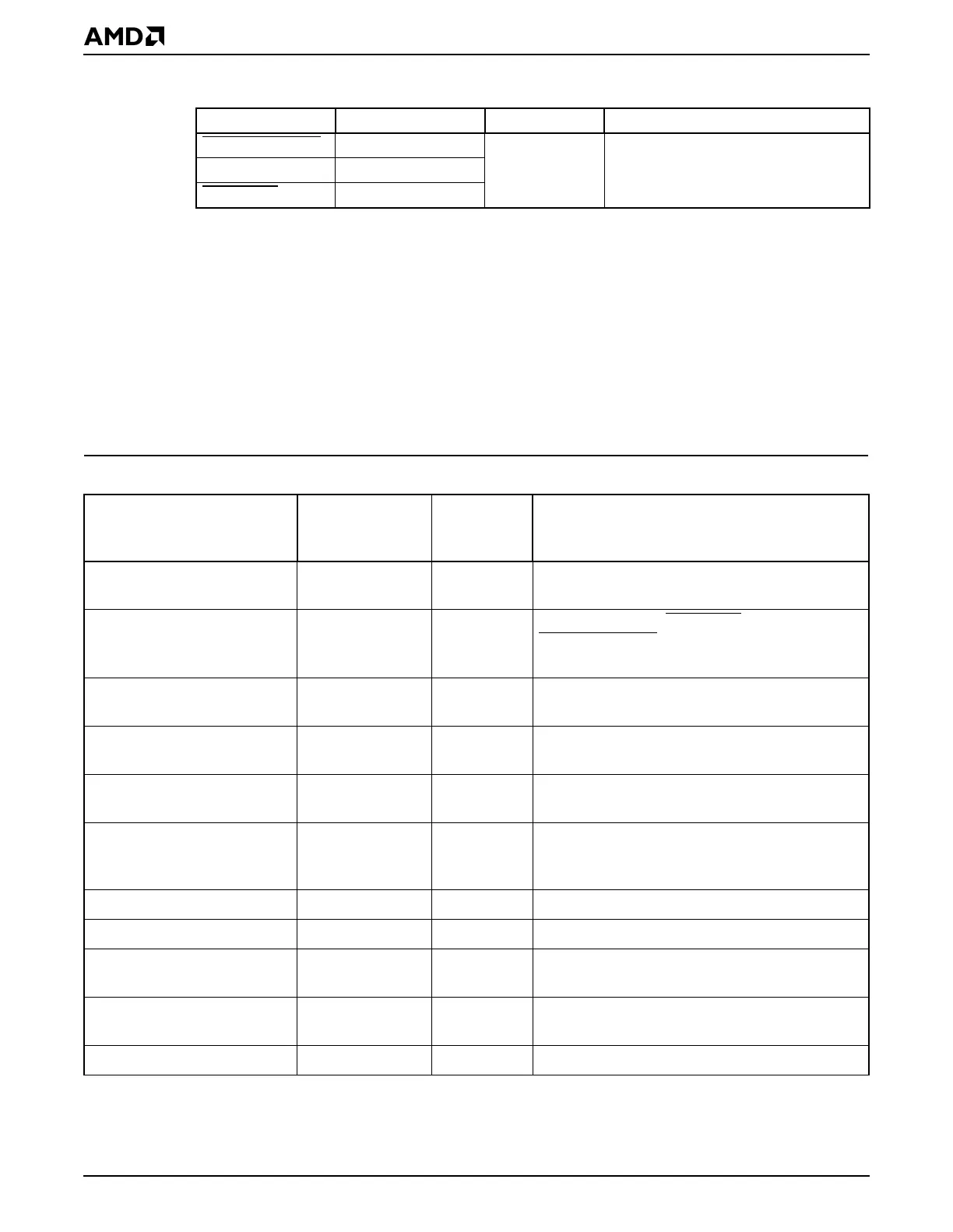

Table 24-2 System Test and Debugging Registers—Memory-Mapped

Register Mnemonic

MMCR

Offset

Address Function

Am5

x

86 CPU Control CPUCTL 02h CPU cache mode select (write-through or write-

back), CPU clock speed

SDRAM Control DRCCTL 10h System test mode (CF_DRAM

, DATASTRB, and

CF_ROM_GPCS

), write buffer test mode

(WBMSTR2–WBMSTR0) enable

ECC Check Code Test ECCCKTEST 23h ECC check code override for test and error

handler development

ECC Single-Bit Error Address ECCSBAD 24h Physical address of the location in SDRAM that

caused a single-bit ECC error

ECC Multi-Bit Error Address ECCMBADD 28h Physical address of the location in SDRAM that

caused a multi-bit ECC error

SDRAM Buffer Control DBCTL 40h Write buffer functions: write buffer enable, read-

ahead enable, write buffer watermark, write

buffer flush.

System Arbiter Control SYSARBCTL 70h System arbitration concurrency mode enable

Address Decode Control ADDDECCTL 80h Write-protect violation interrupt enable

Programmable Address

Region x

PAR0–PAR15 88–C4h Set noncacheable, write-protected, and non-

executable memory regions

GP Echo Mode GPECHO C00h Echo mode enable for monitoring integrated

peripheral accesses on GP bus

Reset Configuration RESCFG D72h AMDebug mode enable

Loading...

Loading...