Programmable Interval Timer

Élan™SC520 Microcontroller User’s Manual 16-3

16.5 OPERATION

The programmable interval timer provides three different timers, or

channels

, and six modes

of operation. Not all channels support every mode.

16.5.1 PIT Channel 0

PIT Channel 0 is used for generating interrupt requests. PIT Channel 0 can be configured

to assert interrupt priority P1 (IRQ0) to allow it to operate in PC/AT-compatible mode. See

Chapter 15, “Programmable Interrupt Controller”, for more information on interrupt steering.

PIT Channel 0 can be configured to assert IRQ0 to allow it to operate in PC/AT-compatible

mode. The gate line is tied High such that PIT Channel 0 operates in four modes only,

modes 0, 2, 3, and 4. Mode 0 is typically used for interrupts, because it remains in the High

state until restarted.

16.5.2 PIT Channel 1

The PIT Channel 1 is used as a general-purpose timer. Its output is hardwired internally to

drive an input of the programmable interrupt controller. See Chapter 15, “Programmable

Interrupt Controller” for more information on interrupt steering.

The gate line is tied High such that PIT Channel 1 also operates in four modes only, modes

0, 2, 3, and 4. Mode 0 is typically used for interrupts, because it remains in the High state

until restarted.

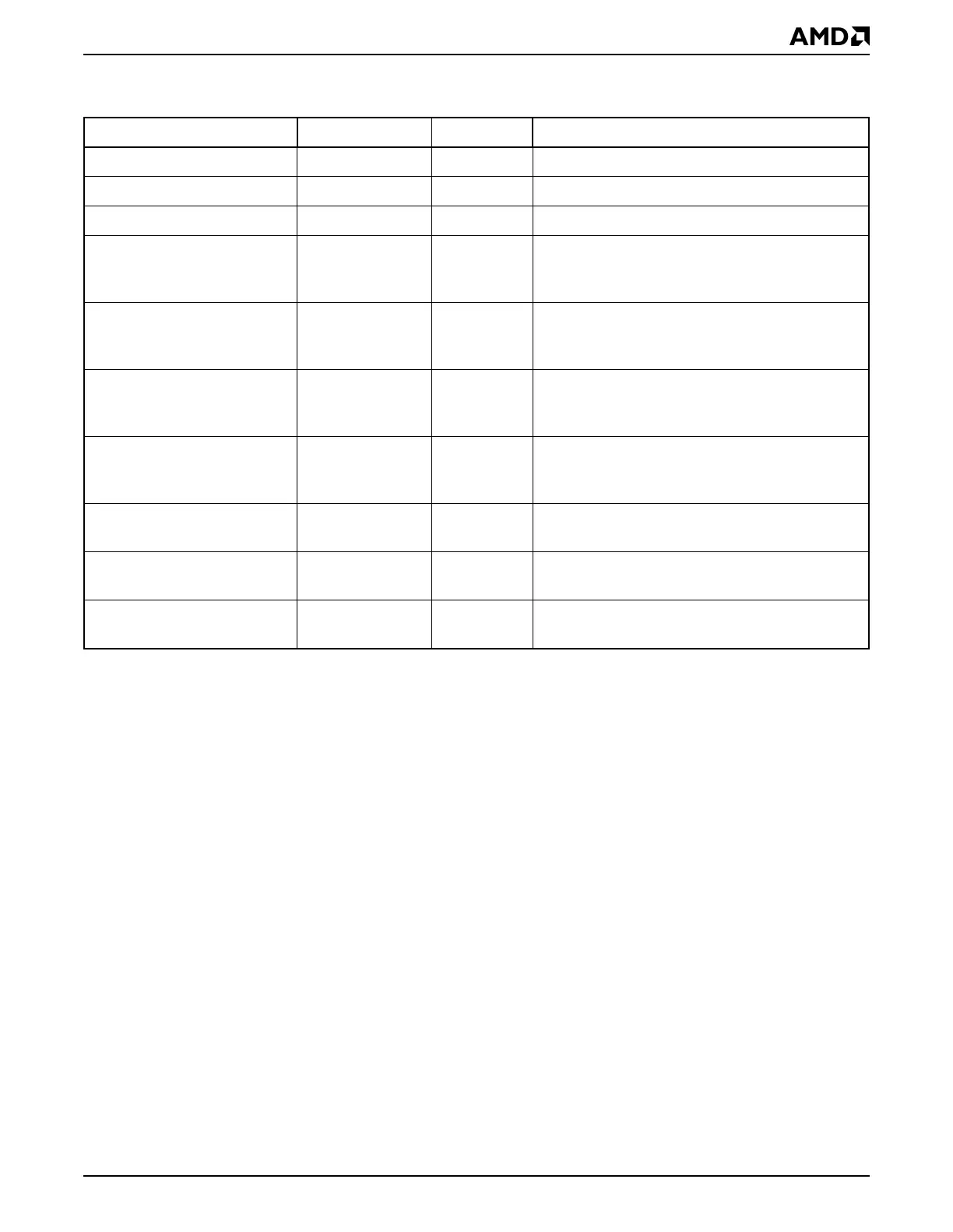

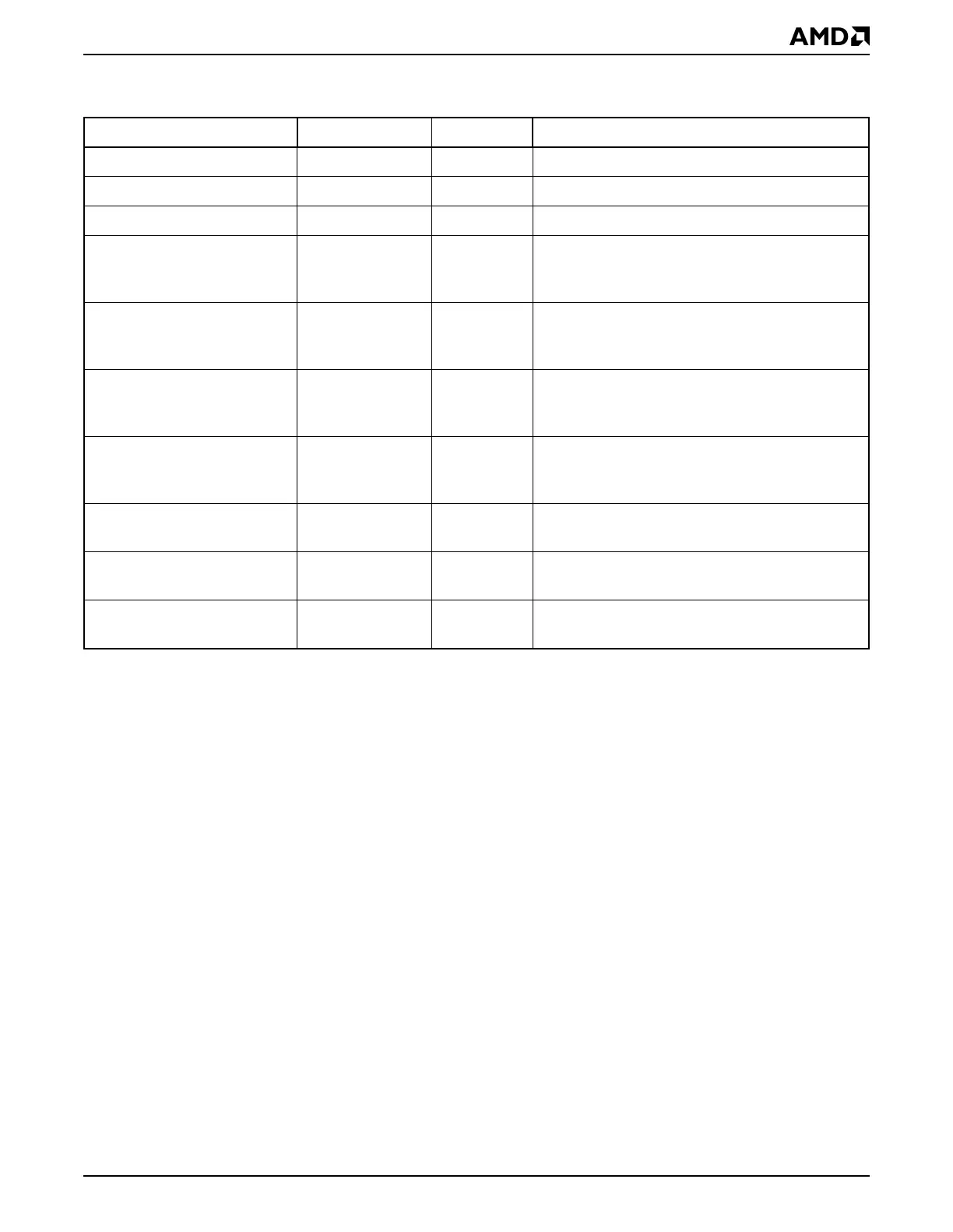

Table 16-3 Programmable Interval Timer Configuration Registers—Direct-Mapped

Register Mnemonic I/O Address Function

PIT Channel 0 Count PIT0CNT 0040h Current count value for Channel 0

PIT Channel 1 Count PIT1CNT 0041h Current count value for Channel 1

PIT Channel 2 Count PIT2CNT 0042h Current count value for Channel 2

PIT 0 Status PIT0STA 0040h Counter mode status, null count, output state,

latch command or read/write control setting, and

BCD setting for Channel 0

PIT 1 Status PIT1STA 0041h Counter mode status, null count, output state,

latch command or read/write control setting, and

BCD setting for Channel 1

PIT 2 Status PIT2STA 0042h Counter mode status, null count, output state,

latch command or read/write control setting, and

BCD setting for Channel 2

PIT Mode Control PITMODECTL 0043h PIT counter select or read-back command, read/

write control or counter latch command, counter

mode, BCD select

PIT Counter Latch Command PITCNTLAT 0043h Control to latch current count of the selected

channel for read-back

PIT Read-Back Command PITRDBACK 0043h Control to latch status and current count of each

channel for read-back

System Control Port B SYSCTLB 0061h PITOUT2 signal enable, status, and Channel 2

gate input control

Loading...

Loading...