Write Buffer and Read Buffer

Élan™SC520 Microcontroller User’s Manual 11-7

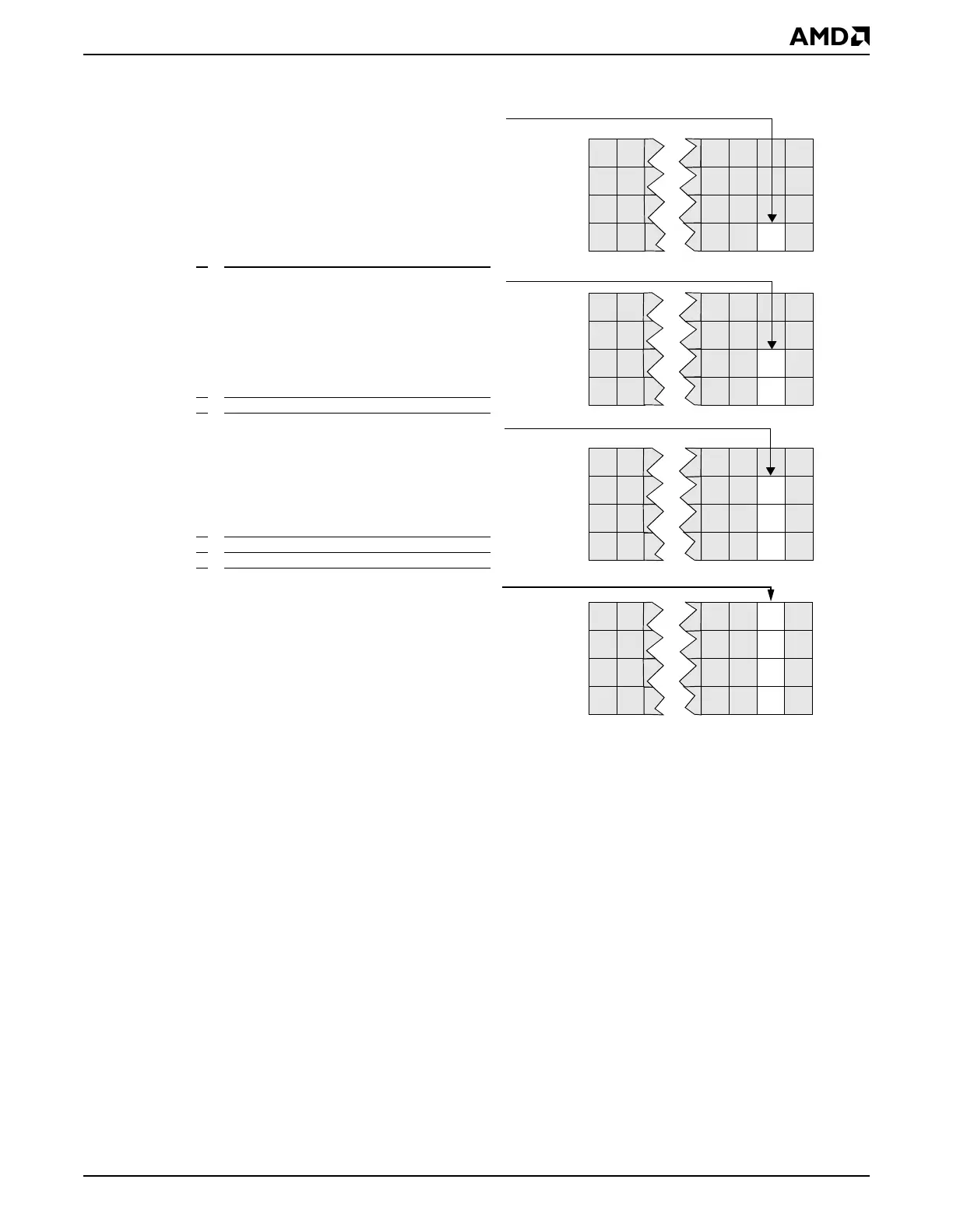

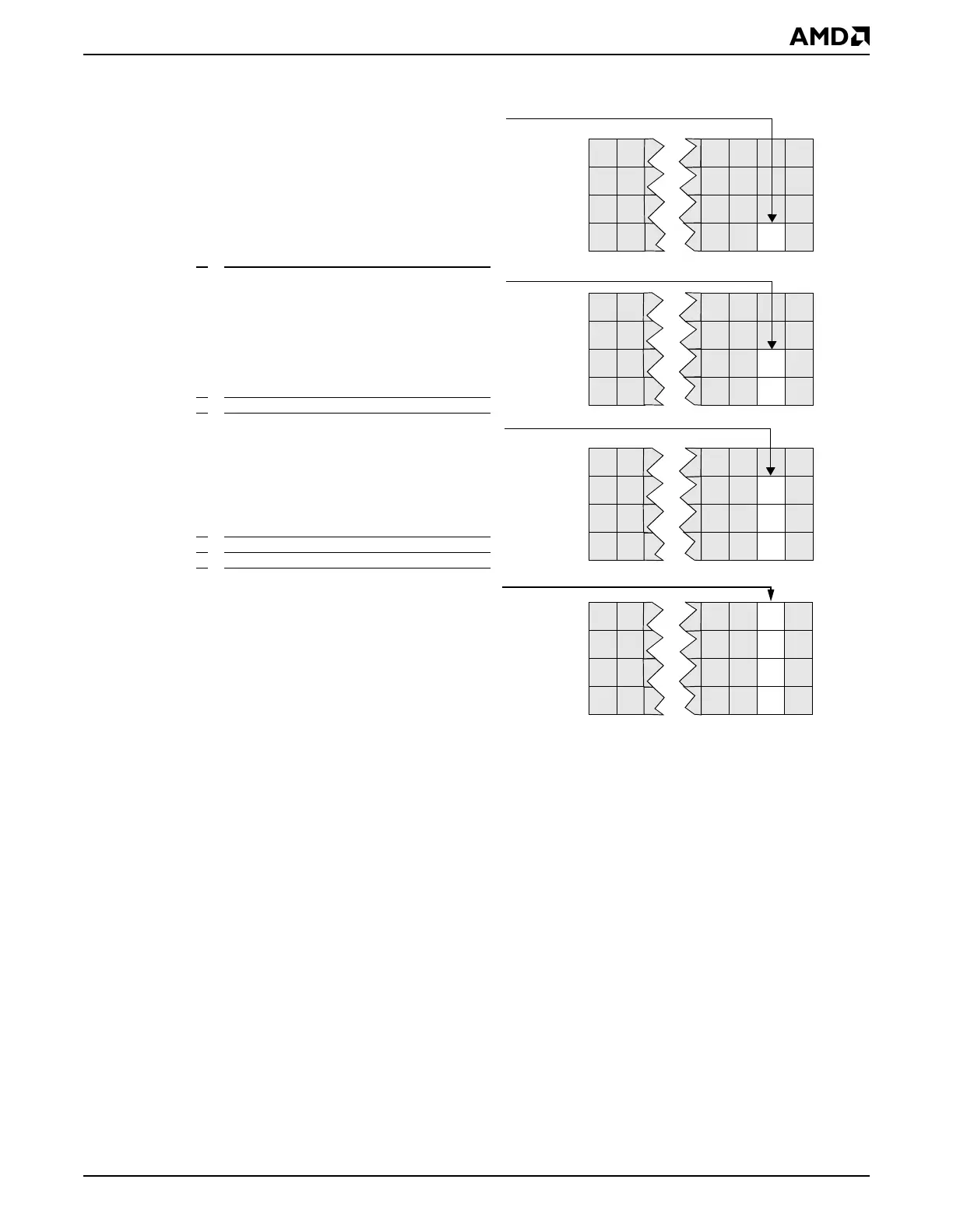

Figure 11-3 Write Buffer Merging Example

88

1. DMA Write, Byte, Adrs 0FBB000, Data 88h

88

01233031

01233031

88

01233031

88

01233031

1.

DMA Write, Byte, Adrs 0FBB000, Data 88h

2. DMA Write, Byte, Adrs 0FBB001, Data 92h

92

92

44

92

44

66

1.

DMA Write, Byte, Adrs 0FBB000, Data 88h

2. DMA Write, Byte, Adrs 0FBB001, Data 92h

3. DMA Write, Byte, Adrs 0FBB002, Data 44h

1.

DMA Write, Byte, Adrs 0FBB000, Data 88h

2. DMA Write, Byte, Adrs 0FBB001, Data 92h

3. DMA Write, Byte, Adrs 0FBB002, Data 44h

4. DMA Write, Byte, Adrs 0FBB003, Data 66h

D[7:0]

D[15:8]

D[23:16]

D[31:24]

D[7:0]

D[15:8]

D[23:16]

D[31:24]

D[7:0]

D[15:8]

D[23:16]

D[31:24]

D[7:0]

D[15:8]

D[23:16]

D[31:24]

Notes:

This example illustrates how four separate write cycles can be “merged” and reduced to only one

doubleword SDRAM write transaction.

Loading...

Loading...