System Arbitration

Élan™SC520 Microcontroller User’s Manual 8-13

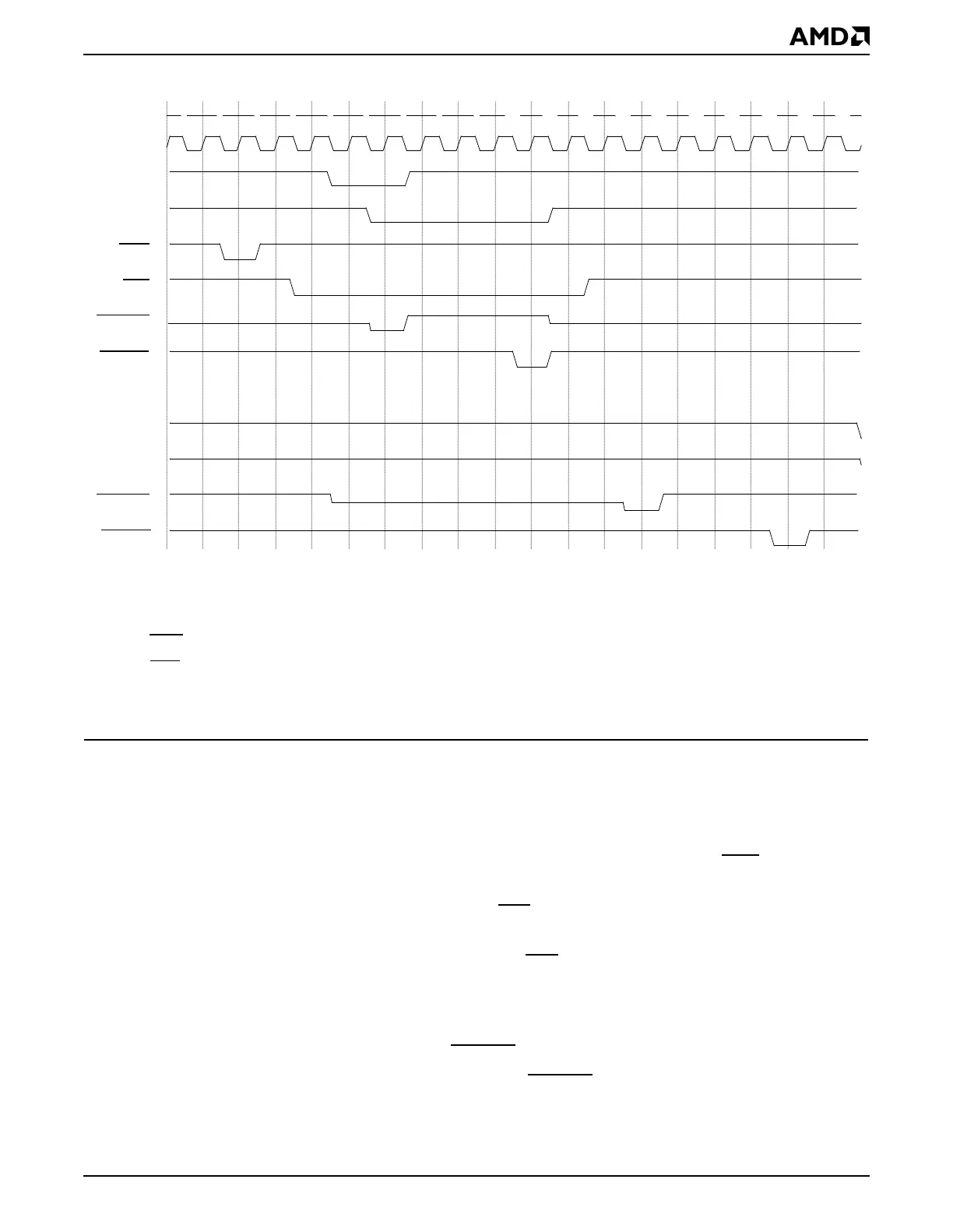

Figure 8-7 CPU Bus Cache Write-Back

Notes:

In Figure 8-7, the CPU bus master signals are labeled mst_xxxx and the Am5

x

86 CPU signals are labeled cpu_xxxx.

The additional internal CPU bus interface signals shown in Figure 8-7 for write-back cycles are

• eads

: External Address Strobe—Asserted by the CPU bus master to initiate a snoop by the Am5

x

86 CPU.

• hitm

: Hit Modified Line—CPU must write back cache line to maintain coherency.

The clk signal denotes the 33-MHz clock source and represents both the CPU clock and the PCI clock. This diagram

does not represent the full synchronization of signals between these clock domains.

The following sequence annotates the CPU bus cache write-back cycle shown in

Figure 8-7.

■ Clock #1: The CPU bus master owns the bus (CPU bus master mst_gnt is asserted,

Am5

x

86 CPU cpu_hold/cpu_hlda are asserted).

■ Clock #2: The CPU bus master initiates an inquire cycle by asserting eads to the Am5

x

86

CPU.

■ Clock #4: The Am5

x

86 CPU asserts hitm to signal that the snoop resulted in a hit to a

modified line. The Am5

x

86 CPU must perform a write-back cycle to maintain coherency.

■ Clock #5: The CPU bus master samples hitm asserted and relinquishes the bus on the

next clock. The CPU bus arbiter deasserts cpu_hold to the Am5

x

86 CPU to allow the

Am5

x

86 CPU to perform the write-back cycle.

■ Clock #6: The Am5

x

86 CPU samples cpu_hold deasserted and deasserts cpu_hlda to

take ownership of the bus. The cpu_ads

signal is asserted to begin the write-back cycle.

■ Clock #7: The CPU bus arbiter samples cpu_ads asserted and asserts hold to the

Am5

x

86 CPU so that no additional cycles are generated after the write-back cycle.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

clk

cpu_hold

cpu_hlda

eads

hitm

cpu_ads

cpu_rdy

mst_req

mst_gnt

mst_ads

mst_rdy

Loading...

Loading...