PCI Bus Host Bridge

9-8 Élan™SC520 Microcontroller User’s Manual

9.5 OPERATION

The PCI host bridge on the ÉlanSC520 microcontroller has the following functionality:

■ Master controller—Allows the Am5

x

86 CPU to be a master on the PCI bus. The Am5

x

86

CPU can generate configuration transactions to configure the PCI host bridge, as well

as all external devices on the PCI bus. The Am5

x

86 CPU can also generate memory

and I/O read and write transactions on the PCI bus.

■ Target controller—Allows external PCI bus masters to access the ÉlanSC520

microcontroller’s SDRAM.

9.5.1 Unsupported PCI Bus Functions

The following list summarizes some of the PCI bus functionality that is not supported in the

ÉlanSC520 microcontroller’s PCI host bridge. These functions are listed as optional in the

PCI bus specification.

■ 66 MHz is not supported.

■ 64-bit data is not supported.

■ 64-bit addressing (dual address cycles) is not supported due to the maximum 32-bit

address space of the Am5

x

86 CPU.

■ Cacheable PCI bus memory (SBDONE, SBO) is not supported.

■ The optional CLKRUN pin is not supported.

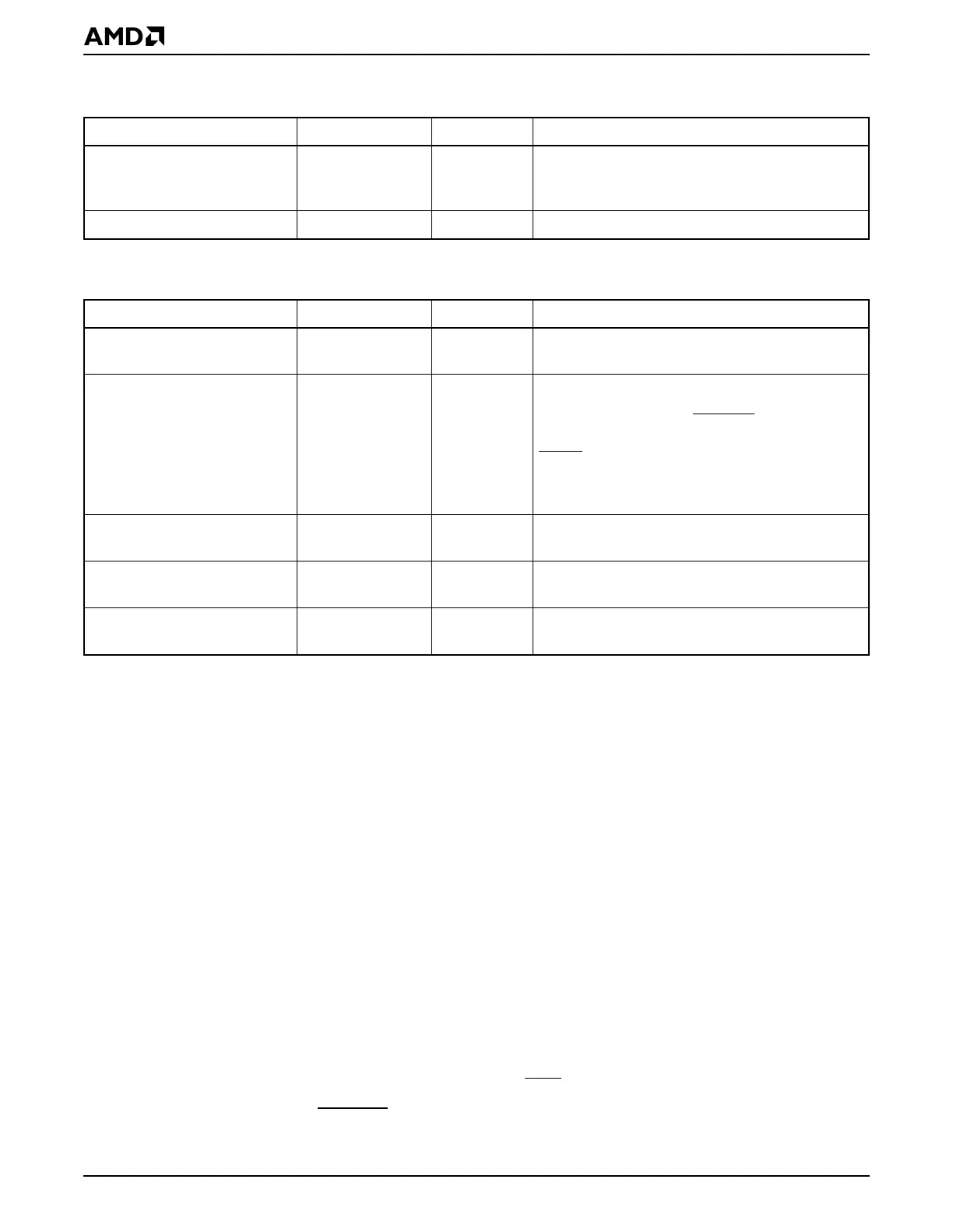

Table 9-2 PCI Host Bridge Registers—Direct-Mapped

Register Mnemonic I/O Address Function

PCI Configuration Address PCICFGADR 0CF8h PCI configuration space enable, bus number,

device number, function number, register

number

PCI Configuration Data PCICFGDATA 0CFCh PCI configuration data

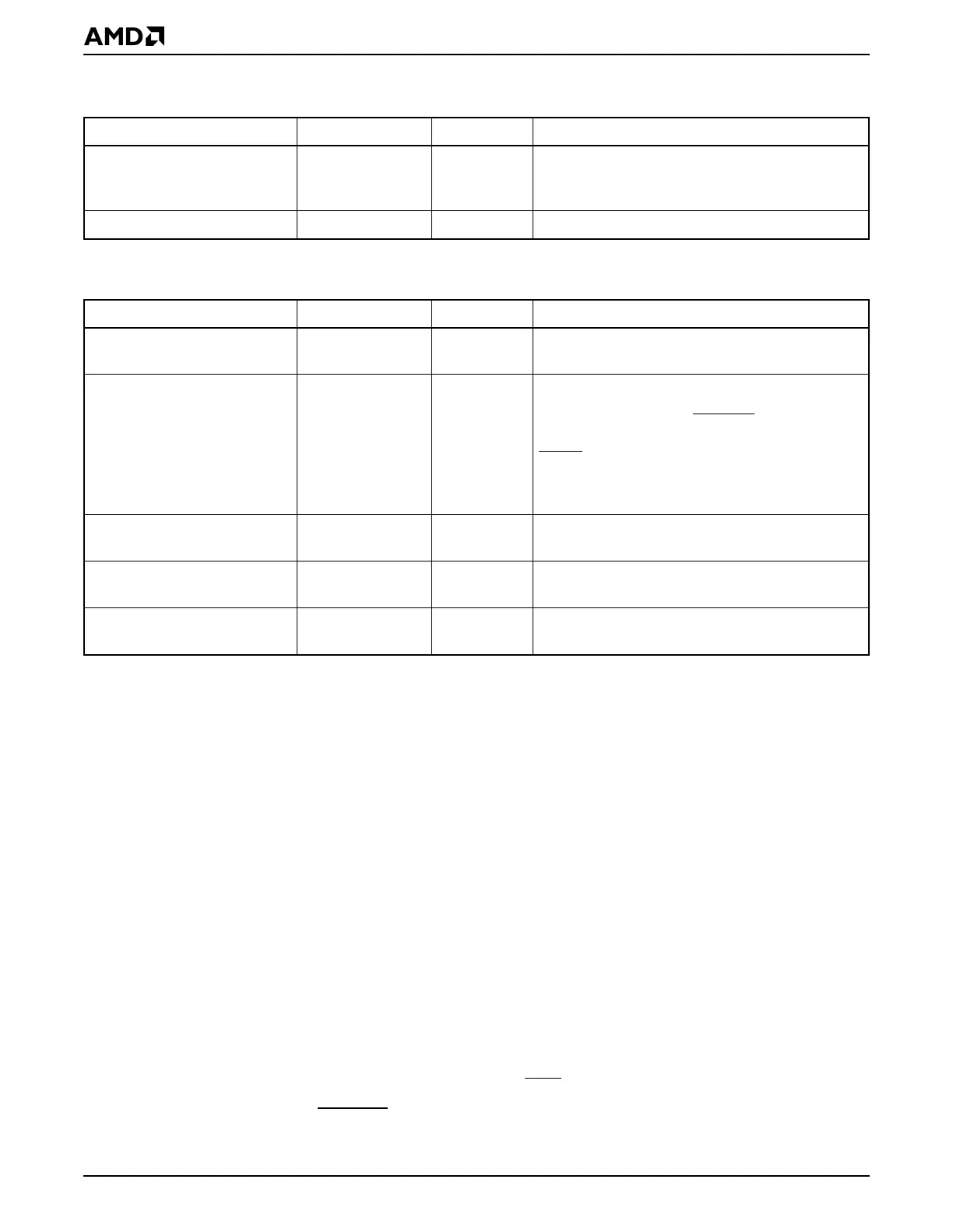

Table 9-3 PCI Host Bridge Registers—PCI Indexed

Register Mnemonic I/O Address Function

Device/Vendor ID PCIDEVID CF8h/CFCh

Index 00h

Device identification, vendor identification

Status/Command PCISTACMD CF8h/CFCh

Index 04h

Parity error detected, signalled system error,

received master abort, received target abort,

signalled target abort, DEVSEL

timing, data

parity reported, fast back-to-back capable,

SERR

enable, parity error response, master

enable, memory access enable, I/O space

enable

Class Code/Revision ID PCICCREVID CF8h/CFCh

Index 08h

Base class code, sub-class code, program

interface type, revision identification

Header Type PCIHEADTYPE CF8h/CFCh

Index 0Eh

PCI configuration space header format

Master Retry Time-Out

PCIMRETRYTO CF8h/CFCh

Index 41h

PCI master retry time-out value

Loading...

Loading...