SDRAM Controller

Élan™SC520 Microcontroller User’s Manual 10-15

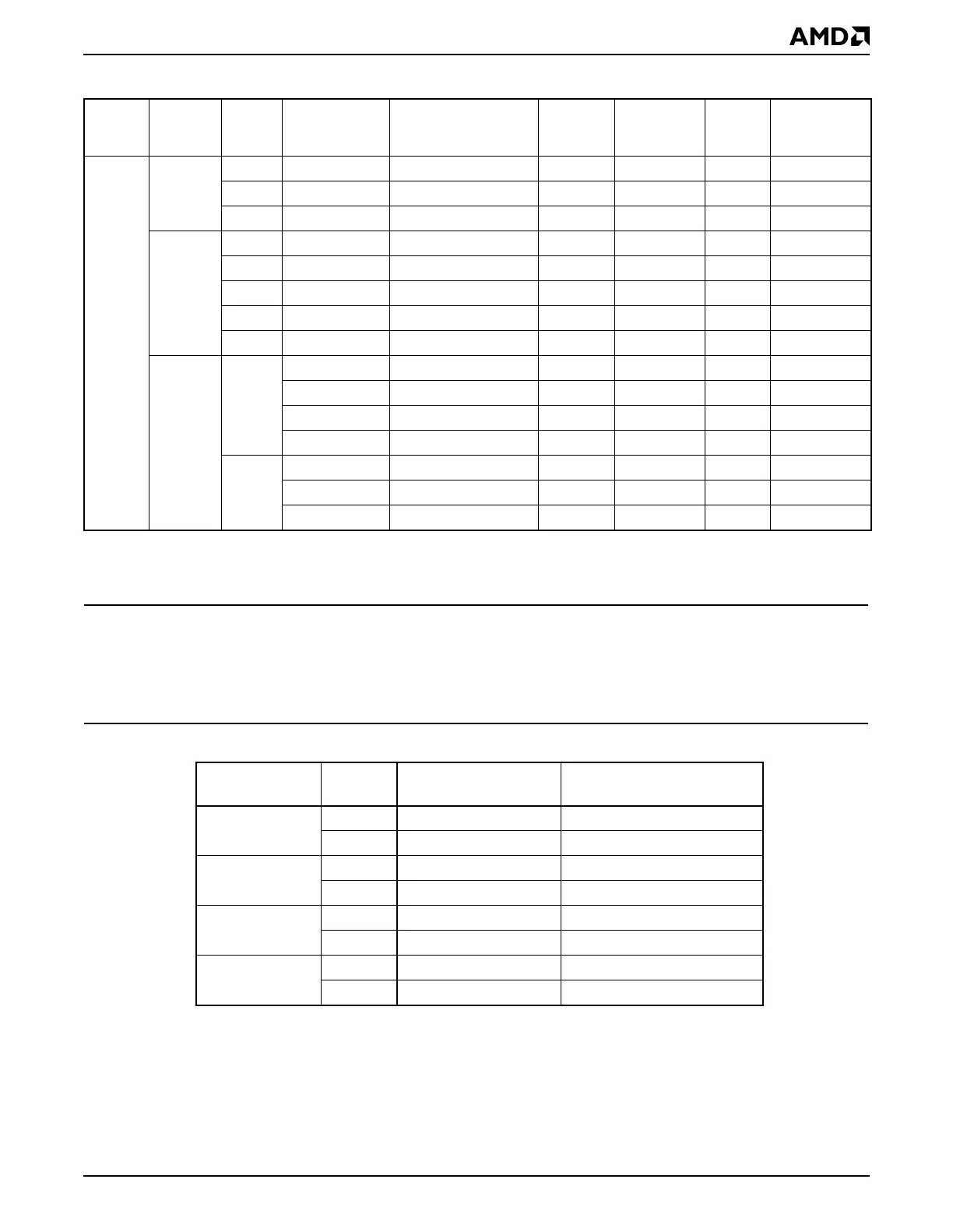

Notes:

Not all device organizations specified in this table are available at the time of this printing.

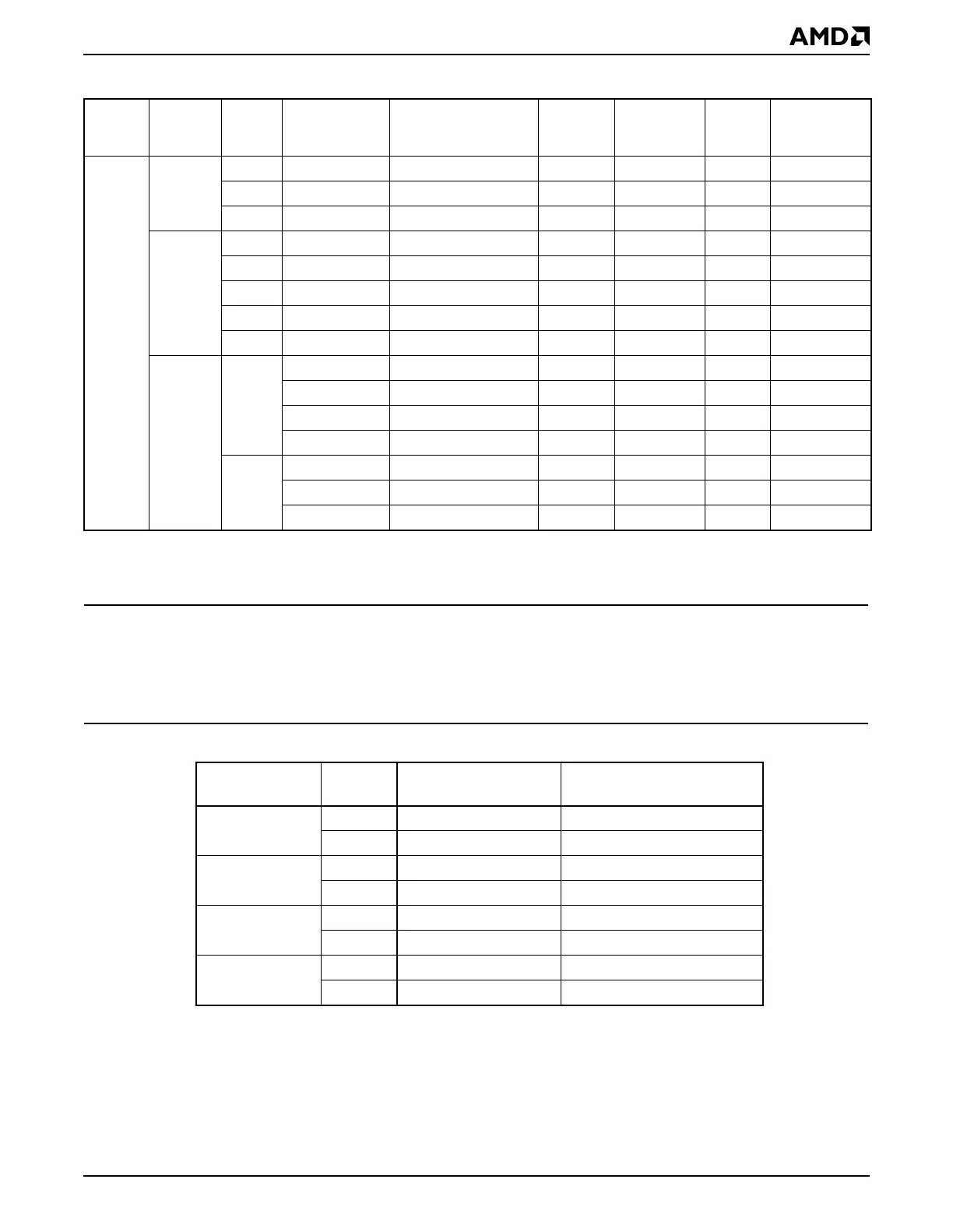

The SDRAM Bank Configuration (DRCCFG) register (MMCR offset 14h) has one bit

(BNKx_BNK_CNT) to specify the internal number of banks and another bit field to specify

the column address width (BNKx_COLWDTH) of the device. Table 10-9 shows suggested

settings for these bit fields, given a device’s column address width and internal bank count.

For example, if Bank 2 is composed of SDRAM devices organized as 2M x 8 x 4 banks (8

Mbyte x 8) with 4096 rows and 512 columns (9-bit), by using Table 10-9, the appropriate

bank configuration for this 4-bank device is 1b for the BNK2_BNK_CNT field and 01b for

the BNK2_COLWDTH field of the SDRAM Bank Configuration (DRCCFG) register.

11-bit 64 Mbit 2 16M x 4 8M x 4 x 2-banks 8 12:11 13-bit 64 Mbytes

8M x 8 4M x 8 x 2-banks 4 11:11 12-bit 32 Mbytes

4 16M x 4 4M x 4 x 4-banks 8 11:11 13-bit 64 Mbytes

128 Mbit 2 32M x 4 16M x 4 x 2-banks 8 13:11 14-bit 128 Mbytes

16M x 8 8M x 8 x 2-banks 4 12:11 13-bit 64 Mbytes

8M x 16 4M x 16 x 2-banks 2 11:11 12-bit 32 Mbytes

4 32M x 4 8M x 4 x 4-banks 8 12:11 14-bit 128 Mbytes

16M x 8 4M x 8 x 4-banks 4 11:11 13-bit 64 Mbytes

256 Mbit 2 64M x 4 32M x 4 x 2-banks 8 14:11 15-bit 256 Mbytes

32M x 8 16M x 8 x 2-banks 4 13:11 14-bit 128 Mbytes

16M x 16 8M x 16 x 2-banks 2 12:11 13-bit 64 Mbytes

8M x 32 4M x 32 x 2-banks 1 11:11 12-bit 32 Mbytes

4 64M x 4 16M x 4 x 4-banks 8 13:11 15-bit 256 Mbytes

32M x 8 8M x 8 x 4-banks 4 12:11 14-bit 128 Mbytes

16M x 16 4M x 16 x 4-banks 2 11:11 13-bit 64 Mbytes

Table 10-9 Column Address Configuration Settings for SDRAM

Column Width Banks

Internal Bank Count

(BNKx_BNK_CNT)

Bank Column Address

(BNKx_COLWDTH)

8-bit 2 0b 00b

41b 00b

9-bit 2 0b 01b

41b 01b

10-bit 2 0b 10b

41b 10b

11-bit 2 0b 11b

41b 11b

Table 10-8 SDRAM Devices Supported with Column Boundary Specification (Continued)

Column

Width Density Banks Organization Device Architecture

Device

Count

per Bank

Dimension

Row: Col

MA/BA

Width

Bank

(32-Bit)

Loading...

Loading...