ROM/Flash Controller

12-4 Élan™SC520 Microcontroller User’s Manual

If the system has ROM devices on both the SDRAM data bus and the GP bus and data

bus buffers are used (on either bus), ROMBUFOE

should be qualified with the appropriate

ROM chip selects and ROMRD

, as needed, to prevent bus conflicts. For example, when

SDRAM buffering is enabled, the SDRAM controller could be attempting to complete posted

writes to the SDRAM. During this time, if the Am5

x

86 CPU performs a read from a ROM

device that is on the GP bus (data bus), the buffer on the SDRAM bus (which isolates the

ROM devices from the SDRAM) activates, unless its buffer control pins were also qualified

with the ROMCSx

pin.

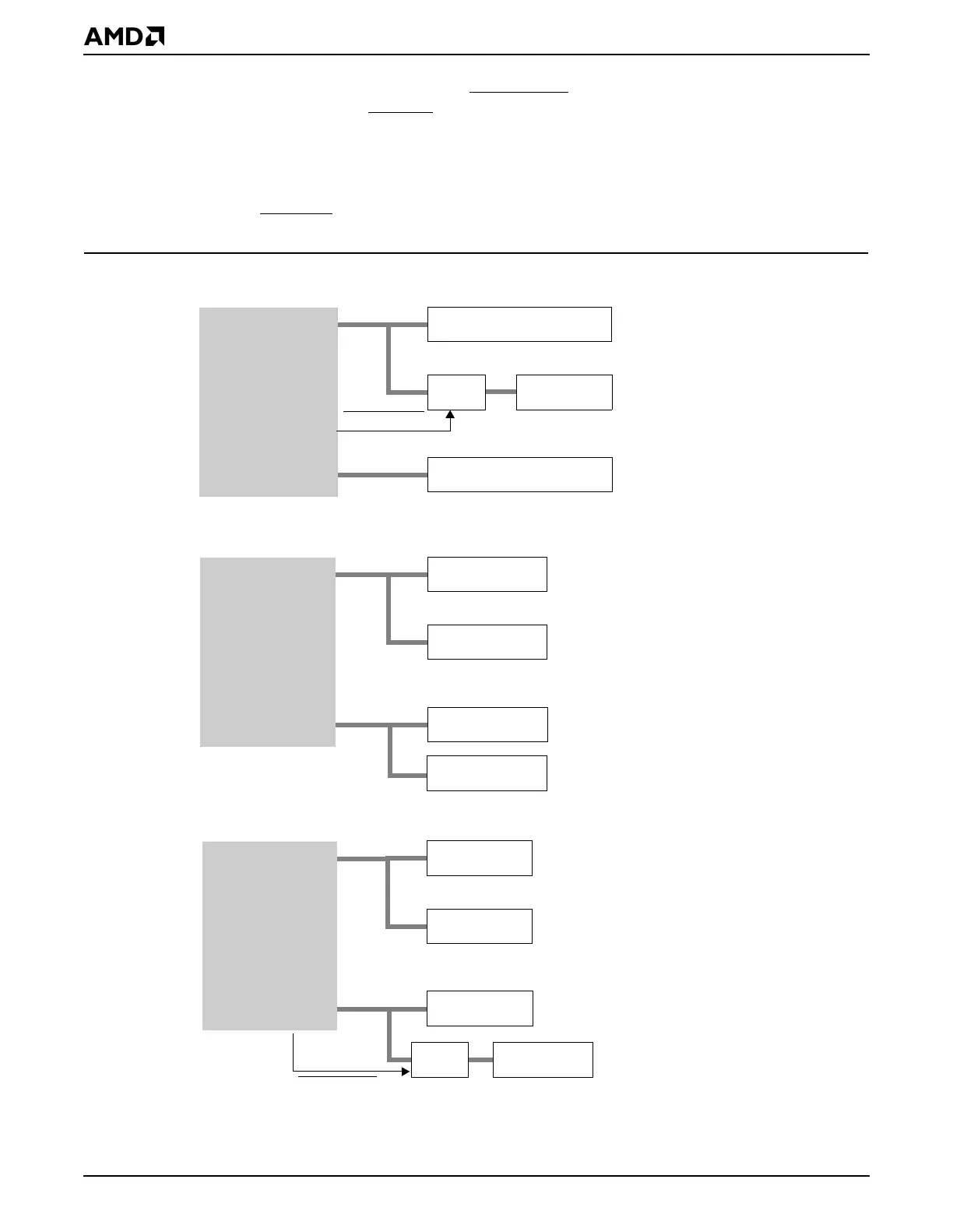

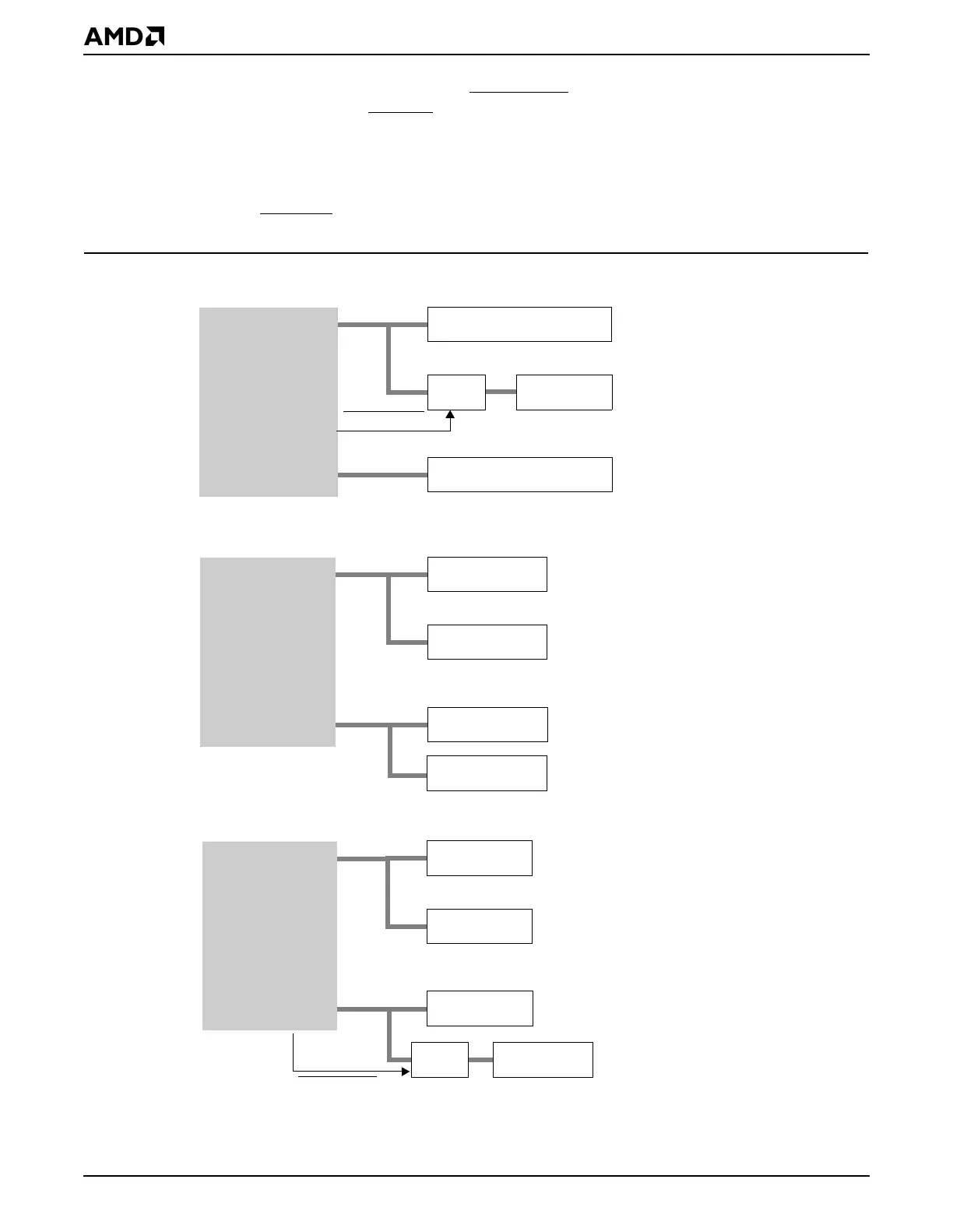

Figure 12-2 Voltage Isolation Examples

3.3-V SDRAM

5-V ROM

5-V Peripheral

Buffer

GP Bus

SDRAM

Bus

3.3-V SDRAM

3.3-V Peripheral

3.3-V ROM

GP Bus

SDRAM

Bus

3.3-V ROM

3.3-V SDRAM

3.3-V ROM

3.3-V ROM

GP Bus

SDRAM

Bus

5-V PeripheralBuffer

ROMBUFOE

GPDBUFOE

Élan™SC520

Microcontroller

Élan™SC520

Microcontroller

Élan™SC520

Microcontroller

Notes:

Both the GP bus and the SDRAM bus can be operated at either 5 V or 3.3 V.

Loading...

Loading...