SDRAM Controller

Élan™SC520 Microcontroller User’s Manual 10-9

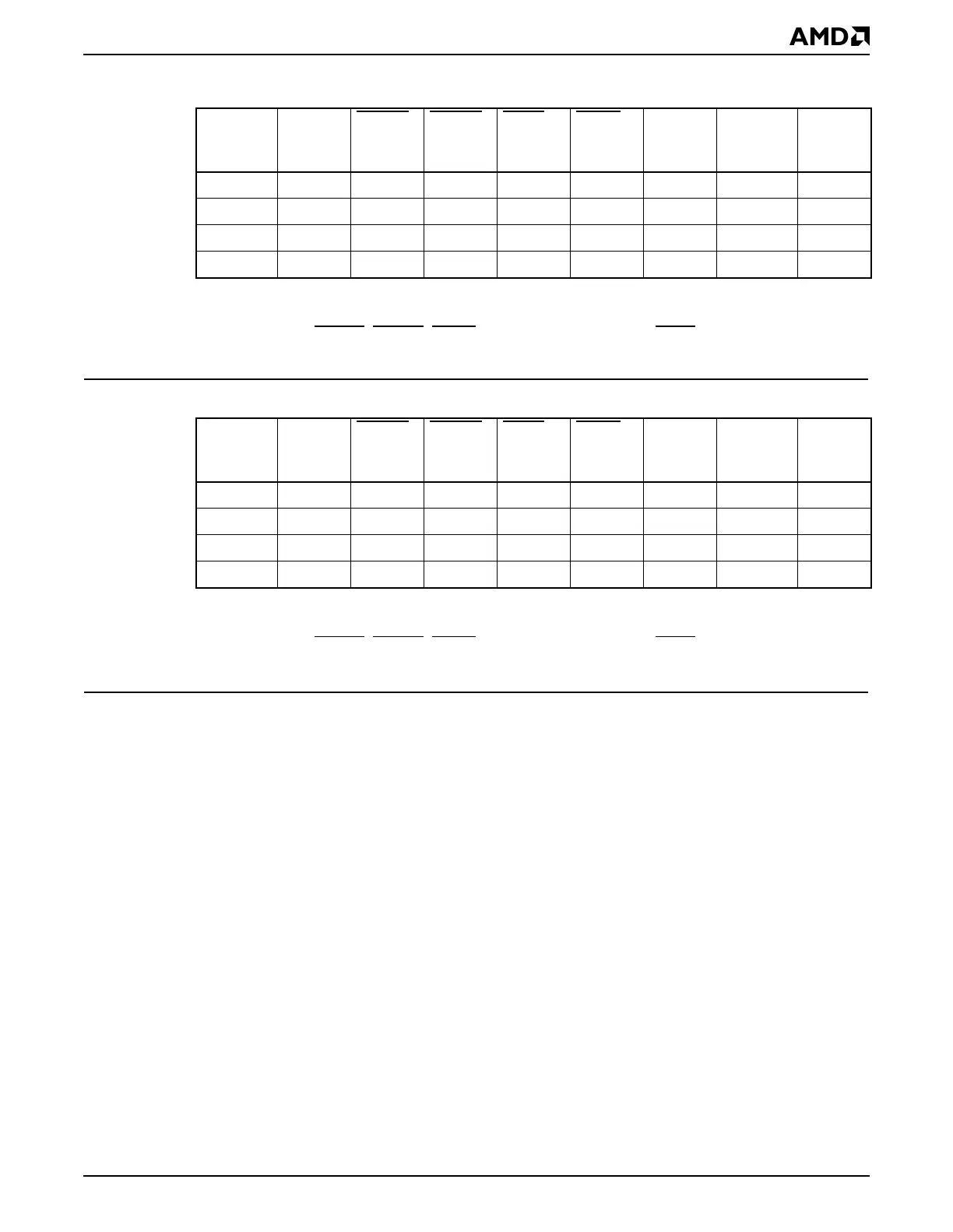

Notes:

Capacitive loads shown in the table above are derived from an estimated SDRAM pin capacitance

value of 5 pF for SRASx

, SCASx, SWEx, MAx, BAx, SDQMx, and SCSx; 4 pF for the CLK signal;

and 6 pF for the MDx signals, per device.

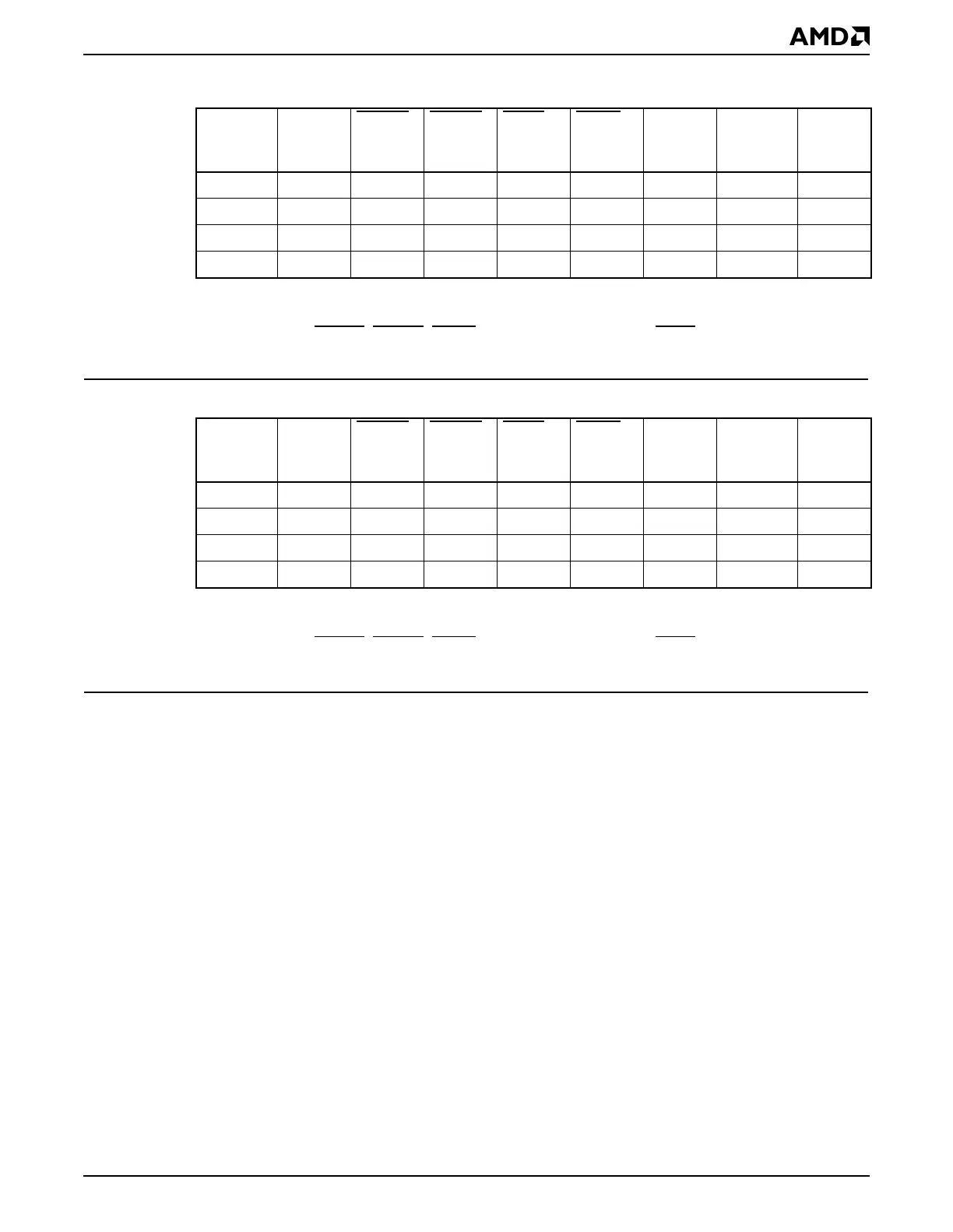

Notes:

Capacitive loads shown in the table above are derived from an estimated SDRAM pin capacitance

value of 5 pF for SRASx

, SCASx, SWEx, MAx, BAx, SDQMx, and SCSx; 4 pF for the CLK signal;

and 6 pF for the MDx signals, per device.

As can be seen clearly from the capacitance tables, as more SDRAM devices are connected

to the SDRAM controller interface signals on the ÉlanSC520 microcontroller, loading on all

these signals increases. Note that the numbers reflect only the actual device capacitance,

and not circuit board trace or buffer capacitance.

The SDRAM controller’s data bus (MD31–MD0) is shared with the ROM/Flash controller.

It is advisable to consider loading issues on the MD31–MD0 bus when both SDRAM and

ROM/Flash devices are installed. Heavy loading by SDRAM and ROM/Flash devices may

slow down the SDRAM timings and cause data corruption.

When ECC devices are not installed, it is advisable to add individual 10-Kohm pulldown

resistors on the MECC6–MECC0 bus to prevent the bus from floating during read access.

Table 10-4 Estimated Capacitance (16-Bit SDRAM Devices)

Number

of 32-Bit

Banks

CLK

Loading

(pF)

SRASx

Loading

(pF)

SCASx

Loading

(pF)

SCSx

Loading

(pF)

SWEx

Loading

(pF)

SDQMx

Loading

(pF)

MAx/BAx

Loading

(pF)

MDx

Loading

(pF)

1 8 10 10 10 10 5 10 6

2 16101010101020 12

3 24202010201530 18

4 32202010202040 24

Table 10-5 Estimated Capacitance (32-Bit SDRAM Devices)

Number

of 32-Bit

Banks

CLK

Loading

(pF)

SRASx

Loading

(pF)

SCASx

Loading

(pF)

SCSx

Loading

(pF)

SWEx

Loading

(pF)

SDQMx

Loading

(pF)

MAx/BAx

Loading

(pF)

MDx

Loading

(pF)

1 4555555 6

2 85555101012

3 12 10 10 5 10 15 15 18

4 16 10 10 5 10 20 20 24

Loading...

Loading...