Reset Generation

Élan™SC520 Microcontroller User’s Manual 6-9

6.5.11 Latency

PRGRESET events must be arbitrated in the SDRAM controller to ensure that the SDRAM

devices are in a state in which data is not lost when the PRGRESET event is propagated.

This arbitration causes the PRGRESET event to be delayed by no more than 32 CPU clock

periods prior to assertion of the internal and external reset signals.

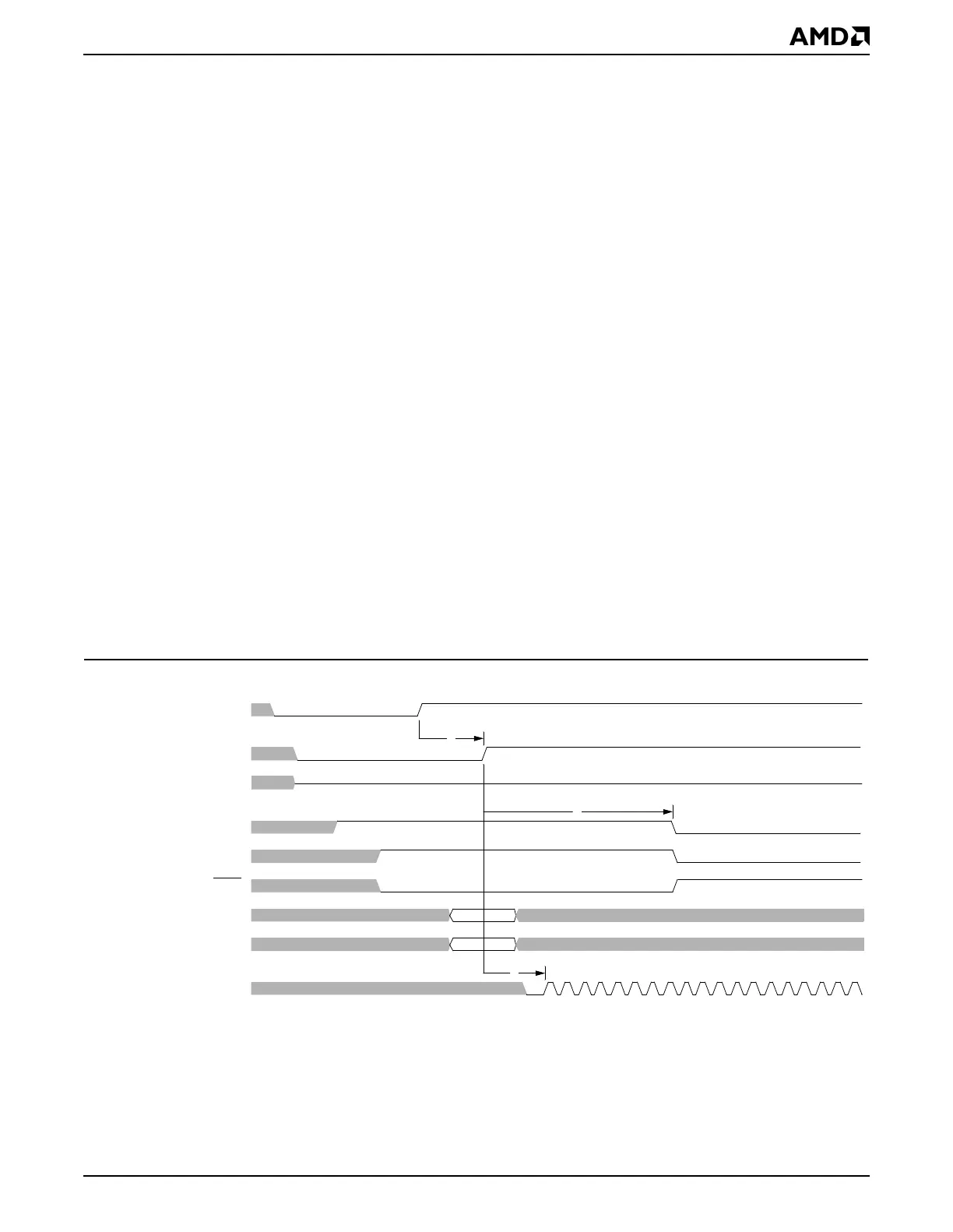

6.6 INITIALIZATION

At power-on reset for the ÉlanSC520 microcontroller, the following sequence of events

occurs.

1. The PWRGOOD pin is deasserted.

2. The power planes come up.

3. Internal CPU, ÉlanSC520 microcontroller internal registers, system GP bus, and PCI

bus resets are asserted.

4. PWRGOOD is asserted. Configuration and system board data are latched on the CFG3–

CFG0 and RSTLD7–RSTLD0 pins, respectively.

5. RTC reset event is generated if the RTC voltage monitor has detected a low RTC battery

condition.

6. Internal PLLs are enabled and clocks become stable (internal PLL startup time is allowed

to pass).

7. Internal CPU, system GP bus, and PCI bus resets are deasserted.

Figure 6-3 shows this sequence. For power-on reset, the PWRGOOD pin must be held

deasserted for the duration of time it takes for the stabilization of the system board power

supply output voltages and the start-up time of the internal 32-kHz and 33-MHz oscillators.

This time is typically on the order of 1 second.

Figure 6-3 Power-On Reset Sequence of Events

Notes:

1.

PWRGOOD

valid from all V

CC

valid (except VCC_RTC) is typically 1 second.

2. PLL start-up time from

PWRGOOD

valid is less than 10 ms.

3. CPU reset and external resets deasserted from PWRGOOD are 10 ms.

4. Internal signals are shown for reference only; they are not available on external pins.

Valid

Valid

1

3

2

ALL V

CC

s

PWRGOOD

PRGRESET

cpu reset

GPRESET

RST

CFG3–CFG0

RSTLD7–RSTLD0

Internal Clocks

Loading...

Loading...