System Arbitration

Élan™SC520 Microcontroller User’s Manual 8-9

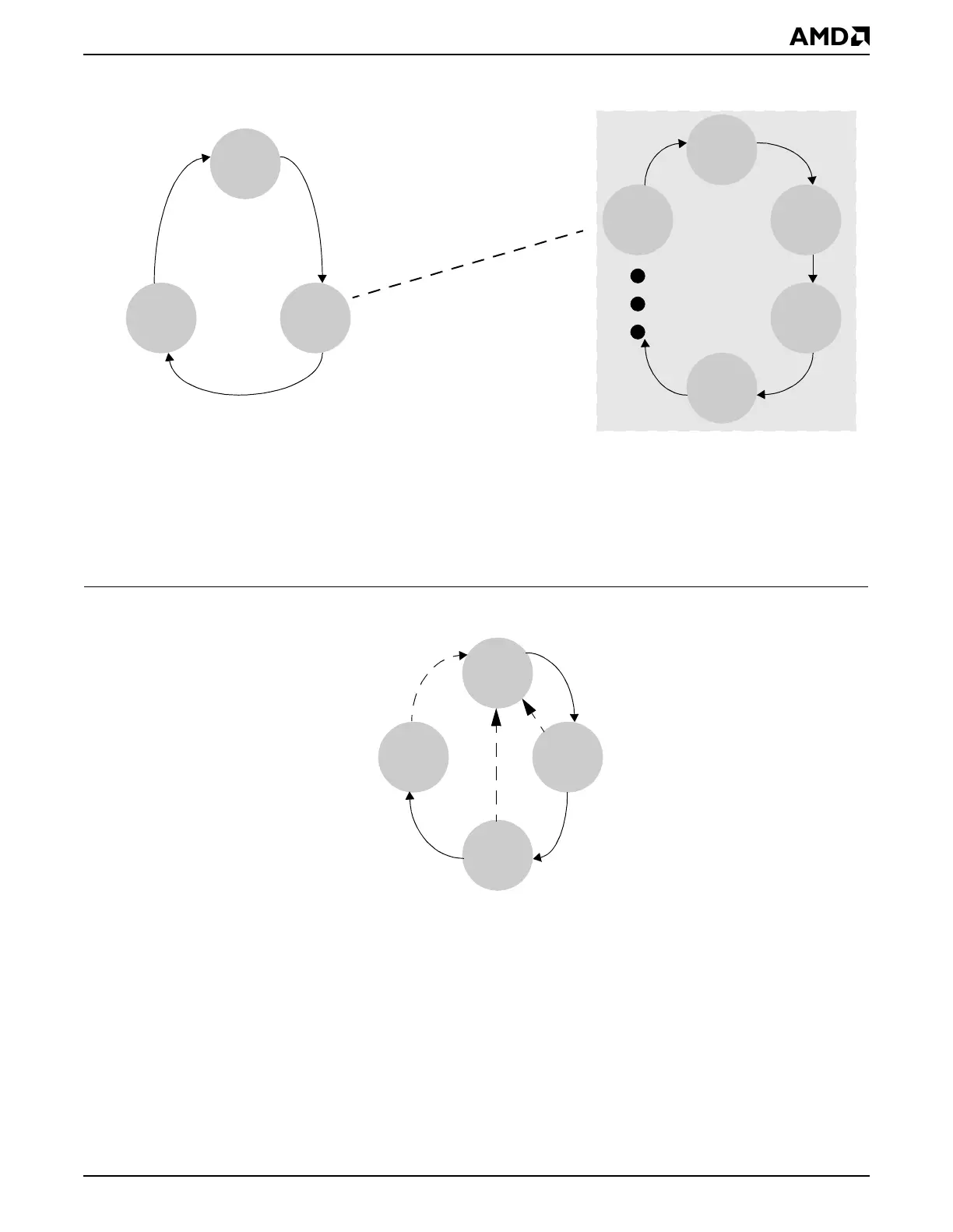

Figure 8-4 External PCI Master Arbitration Queues

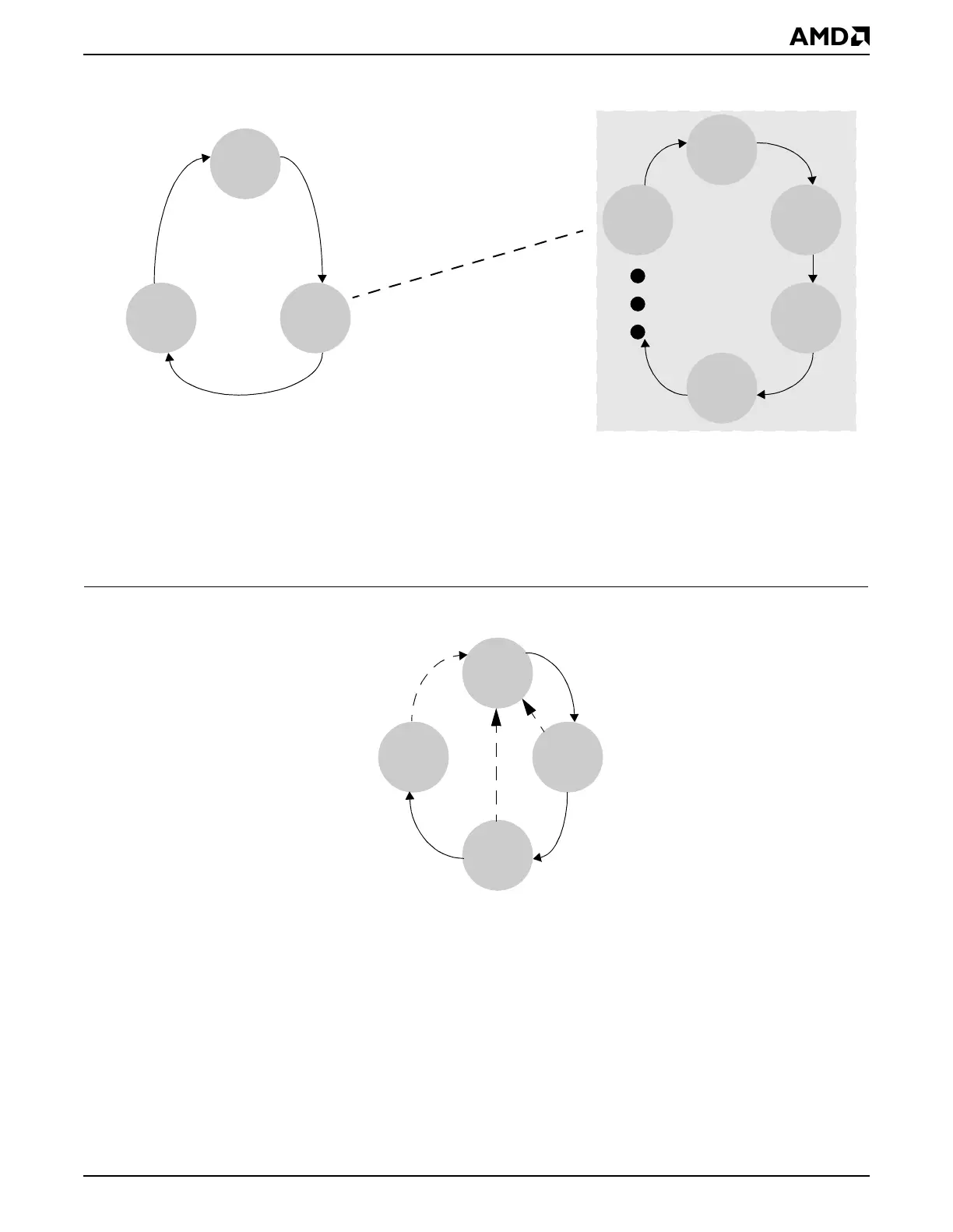

Figure 8-5 Host Bridge Master Arbitration Queue

HP0

HP1

LPx

LP0

LP1

LP2

LP3

LPn

High-Priority Queue

Low-Priority Queue

Notes:

HP0, HP1: High-priority masters

LP0, LP1, LP2, LP3, ..., LPn: Low-priority masters

LPx: Current low-priority master selected

Priority: HP0, HP1, LP0, HP0, HP1, LP1, HP0, HP1, LP2, HP0, HP1, LP3, ..., HP0, HP1, LPn

CPU

Ext

PCI

PCI

Ext

PCI

Ext

Notes:

The PCI bus arbiter is configurable to grant the bus to the host bridge after every 1, 2, or 3 external

PCI transactions.

Priority configured for 1: CPU, Ext PCI, CPU, Ext PCI, ...

Priority configured for 2: CPU, Ext PCI, Ext PCI, CPU, Ext PCI, Ext PCI, ...

Priority configured for 3: CPU, Ext PCI, Ext PCI, Ext PCI, CPU, Ext PCI, Ext PCI, Ext PCI, ...

Loading...

Loading...