ROM/Flash Controller

Élan™SC520 Microcontroller User’s Manual 12-11

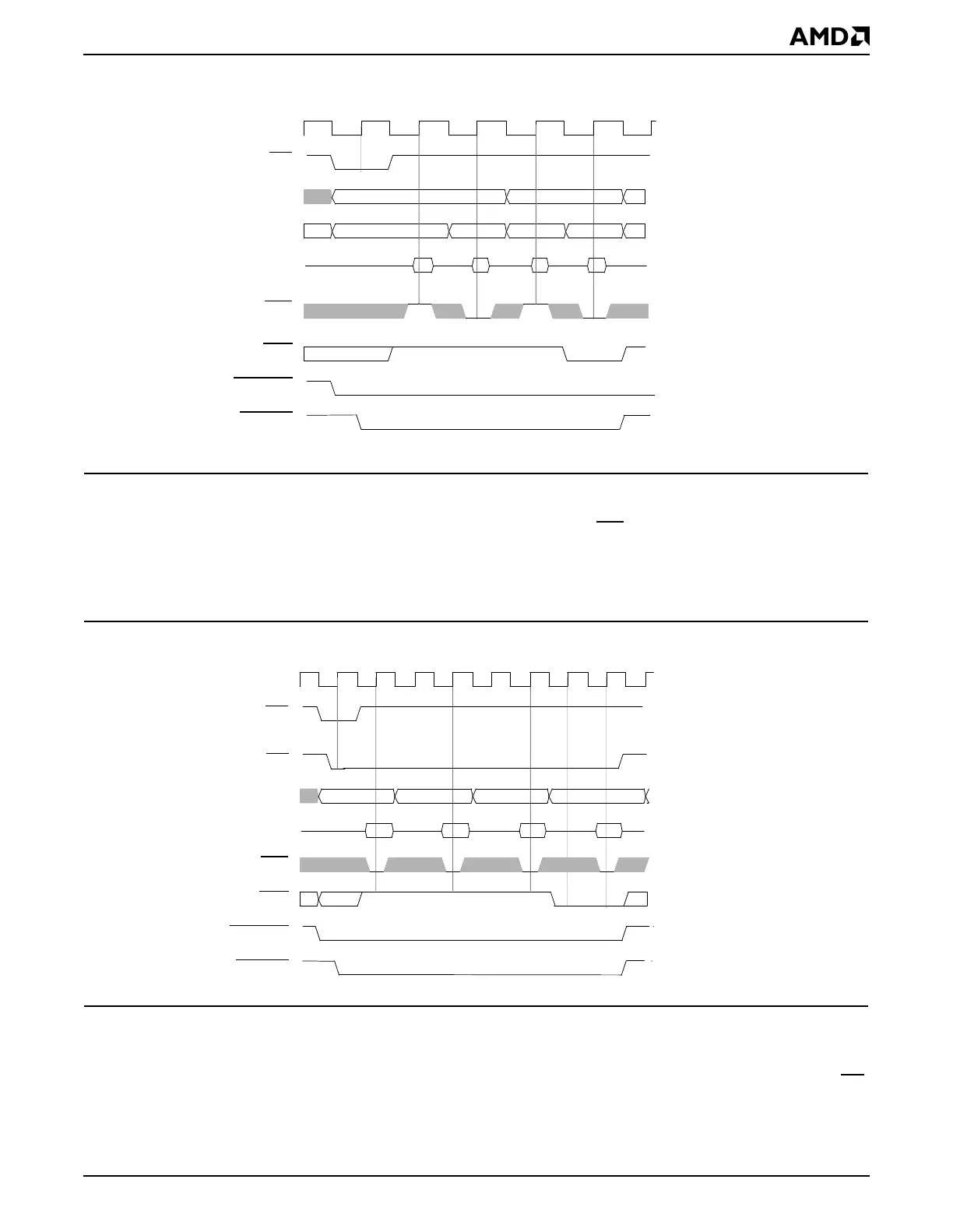

Figure 12-9 Page Access for Fetching Two Doublewords from a 16-Bit ROM

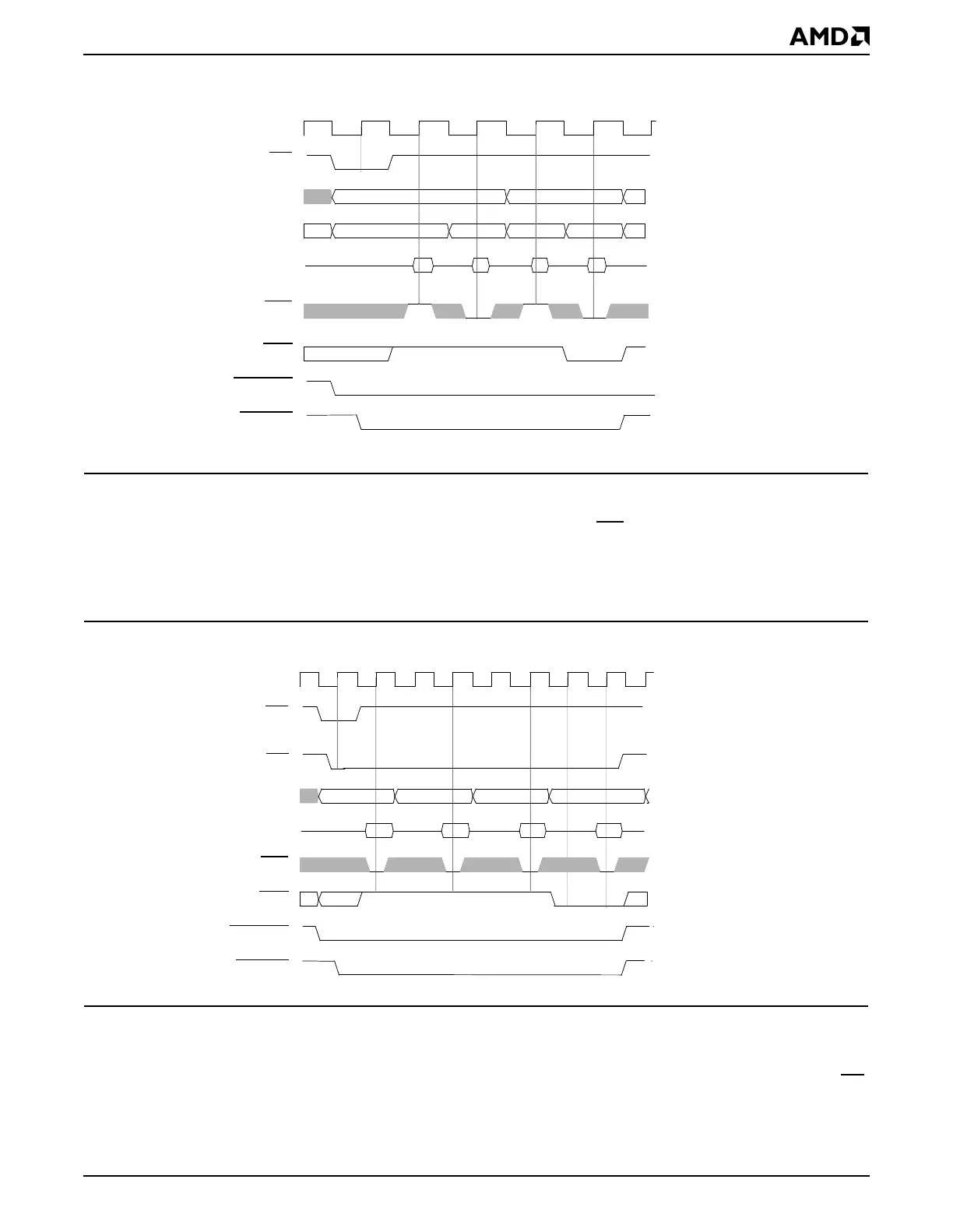

12.5.3.3 Cache-Line Fill

If a memory section is accessed that is cacheable, the ken signal is asserted to the Am5

x

86

CPU indicating a cache-line fill operation. This causes the Am5

x

86 CPU to read four

doublewords (16 bytes) and leads to multiple ROM accesses. A cache-line fill to a 32-bit

ROM is depicted in Figure 12-10.

Figure 12-10 Cache-Line Fill (Fetching Four Doublewords from a 32-Bit ROM)

12.5.3.4 Writing to Flash Devices

The ÉlanSC520 microcontroller supports writable Flash devices. Since Flash devices are

not intended for random write accesses, no burst-write operations are supported, i.e., rdy

is returned to the Am5

x

86 CPU. Figure 12-11 shows a write cycle to a Flash ROM. In

addition, for write accesses, the ROM controller bus-sizes ROM accesses to indicate the

start cycle

- - - C

02

0 2

- - - 8

CPU clock

ads

GPA25–GPA2

GPA1–GPA0

GPD15–GPD0, or

brdy

blast

BOOTCS

ROMRD

MD15–MD0

- - - C - - - 8 - - - 4

- - - 0

CPU clock

ads

ken

GPA25–GPA0

MD31–MD0

brdy

blast

BOOTCS

ROMRD

Loading...

Loading...