Élan™SC520 Microcontroller User’s Manual 7-1

CHAPTER

7

Am5

X

86

®

CPU

7.1 OVERVIEW

The ÉlanSC520 microcontroller has an integrated Am5

x

86 CPU core. The features of the

Am5

x

86 CPU include:

■ Operation at 100 MHz or 133 MHz, with a 33-MHz bus interface

■ 16-Kbyte unified cache configurable for either write-back or write-through cache mode

■ Integrated floating point unit (ANSI/IEEE 754 compliant)

■ On-chip debug support. See Chapter 26, “AMDebug™ Technology”, for more

information.

7.2 BLOCK DIAGRAM

Figure 7-1 shows a block diagram of the Am5

x

86 CPU.

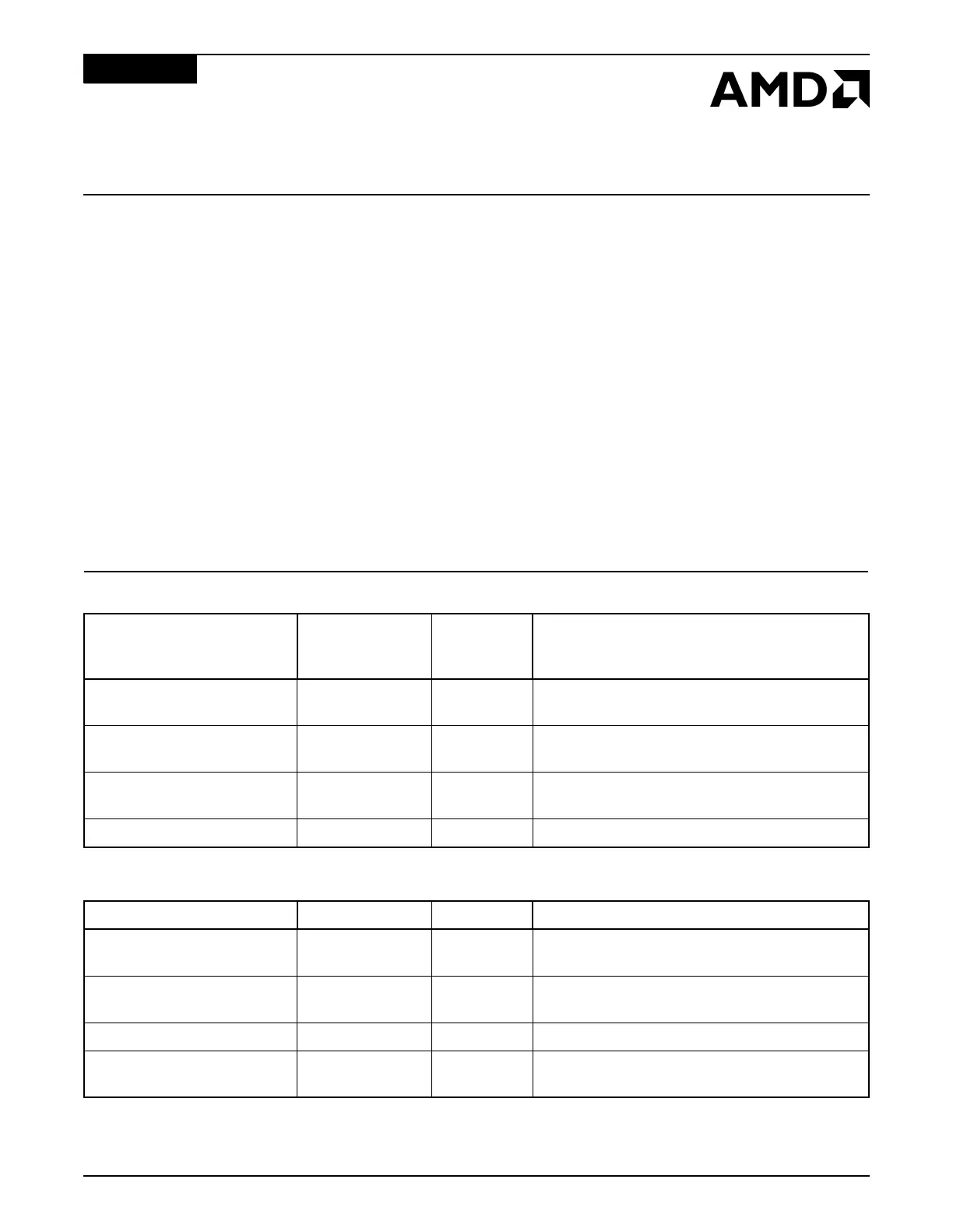

7.3 REGISTERS

The Am5

x

86 CPU is controlled by the registers listed in Table 7-1 and Table 7-2.

Table 7-1 Am5

x

86® CPU Registers—Memory-Mapped

Register Mnemonic

MMCR

Offset

Address Function

ÉlanSC520 Microcontroller

Revision ID

REVID 00h Product identification, major and minor stepping

level

Am5

x

86 CPU Control CPUCTL 02h CPU cache mode (write-through or write-back),

CPU clock speed control

Floating Point Error Interrupt

Mapping

FERRMAP D46h Floating point error interrupt mapping

Reset Status RESSTA D74h Reset source status: CPU shutdown (soft reset)

Table 7-2 Am5

x

86® CPU Registers—Direct-Mapped

Register Mnemonic I/O Address Function

SCP Data Port SCPDATA 60h System Control Processor (SCP) data write, a20

gate command emulation

SCP Command Port SCPCMD 64h SCP command write, a20 gate command

emulation, CPU reset command emulation

System Control Port A SYSCTLA 92h CPU soft reset generation, alternate a20 control

Floating Point Error Interrupt

Clear

FPUERRCLR F0h Clear FPU error interrupt

Loading...

Loading...