Synchronous Serial Interface

22-2 Élan™SC520 Microcontroller User’s Manual

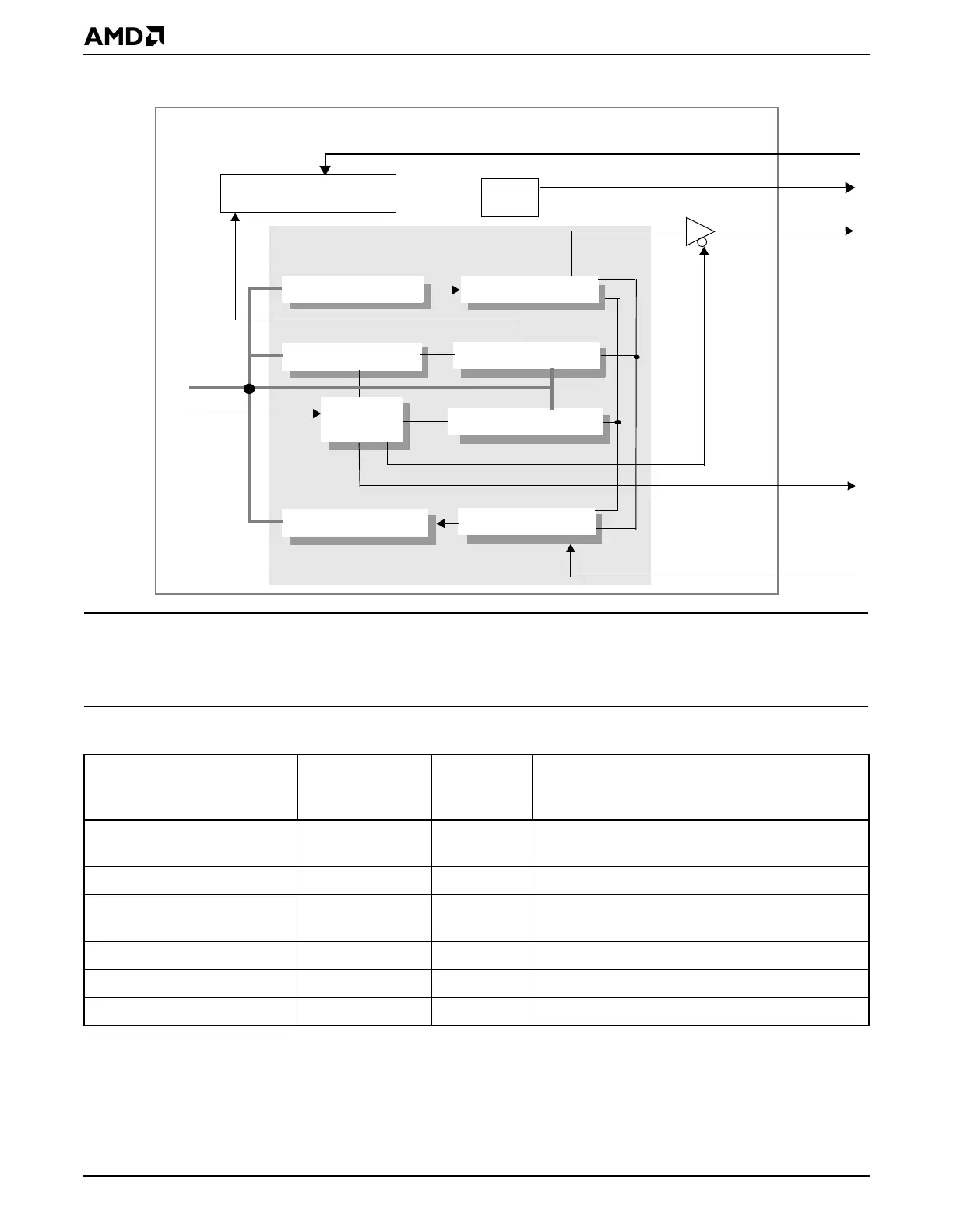

Figure 22-1 SSI Block Diagram

22.4 REGISTERS

The memory-mapped registers shown in Table 22-1 are used to configure the SSI.

Table 22-1 Synchronous Serial Interface Registers—Memory-Mapped

Register Mnemonic

MMCR

Offset

Address Function

SSI Control SSICTL CD0h SSI clock speed, interrupt enable, clock phase,

clock idle state, bit order

SSI Transmit SSIXMIT CD1h Byte or data to be shifted out to SSI_DO pin

SSI Command SSICMD CD2h Transfer command to be executed: transmit,

receive, or simultaneous transmit/receive

SSI Status SSISTA CD3h Busy status, transaction complete status

SSI Receive SSIRCV CD4h Byte or data shifted in from SSI_DI pin

SSI Interrupt Mapping SSIMAP D41h SSI interrupt mapping

Block

SSI Control Register

SSI Transmit Register

SSI Receive Register

SSI Command Register

SSI_DO

SSI_DI

SSI_CLK

SSI Status Register

PIOx

Generation

SSI Clock

shift register

shift register

Programmable Interrupt

Controller (PIC)

Internal

PIO

GP Bus

33-MHz

Clock

SSI

GPIRQx

ssi_irq

tri_do

Élan™SC520 Microcontroller

Loading...

Loading...