PCI Bus Host Bridge

9-24 Élan™SC520 Microcontroller User’s Manual

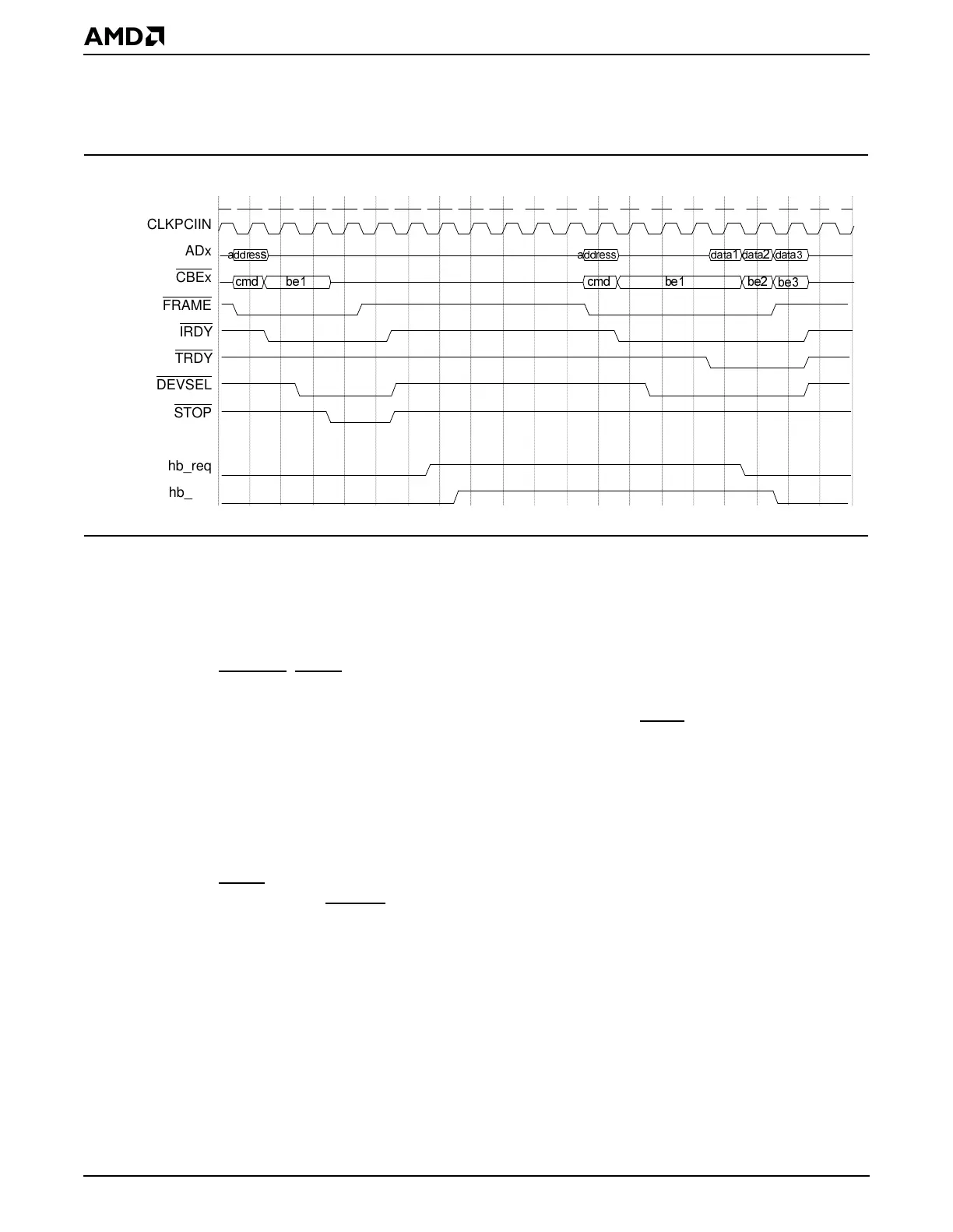

9.5.4.9.2 External PCI Master SDRAM Read (Delayed Transaction)

Figure 9-15 shows an external PCI bus master read transaction to the ÉlanSC520

microcontroller’s SDRAM.

Figure 9-15 External PCI Master SDRAM Read (Delayed Transaction)

The following sequence annotates the external PCI master SDRAM read shown in

Figure 9-15.

■ Clock #1: An external PCI bus master initiates a read transaction to ÉlanSC520

microcontroller’s SDRAM.

■ Clock #3: The PCI host bridge target controller accepts the transaction by asserting

DEVSEL

. TRDY is not asserted, because there is no data in the target read FIFO (this

is a new transaction).

■ Clock #4: The PCI host bridge target controller asserts STOP, signaling a retry to the

external PCI bus master. Because no data was transferred, the external PCI bus master

is required to retry the transaction. (This figure assumes that the ÉlanSC520

microcontroller is configured for automatic delayed transactions.) The host bridge

latches the transaction information and will prefetch the requested read data. This is

now a delayed transaction, and the PCI bus master is required to relinquish bus

ownership and re-arbitrate to retry the cycle. If there is already a previous delayed

transaction pending, the current transaction will not be latched. Note that, in this example,

STOP

is asserted for two clock periods, because a target is required to keep this signal

asserted until FRAME

is deasserted.

■ Clock #7: The PCI host bridge has synchronized the delayed transaction request and

requests access to the SDRAM controller to prefetch the data requested by the external

PCI master.

■ Clock #8: The CPU bus is granted to the PCI host bridge, and the PCI bus data can be

read from SDRAM. The hb_gnt signal may be delayed if the Am5

x

86 CPU or GP-DMA

controller is accessing SDRAM. The host bridge prefetches up to the next cache line in

response to a memory-read or memory-read-line command and up to 64 doublewords

in response to a memory-read-multiple command.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

FPG EH

DGGUHV

V

DGGUHVV

FPG

GDWD

GDWD

GDWD

EH

EH

EH

CLKPCIIN

ADx

CBEx

FRAME

IRDY

TRDY

DEVSEL

STOP

hb_req

hb_gnt

Loading...

Loading...