System Initialization

3-6 Élan™SC520 Microcontroller User’s Manual

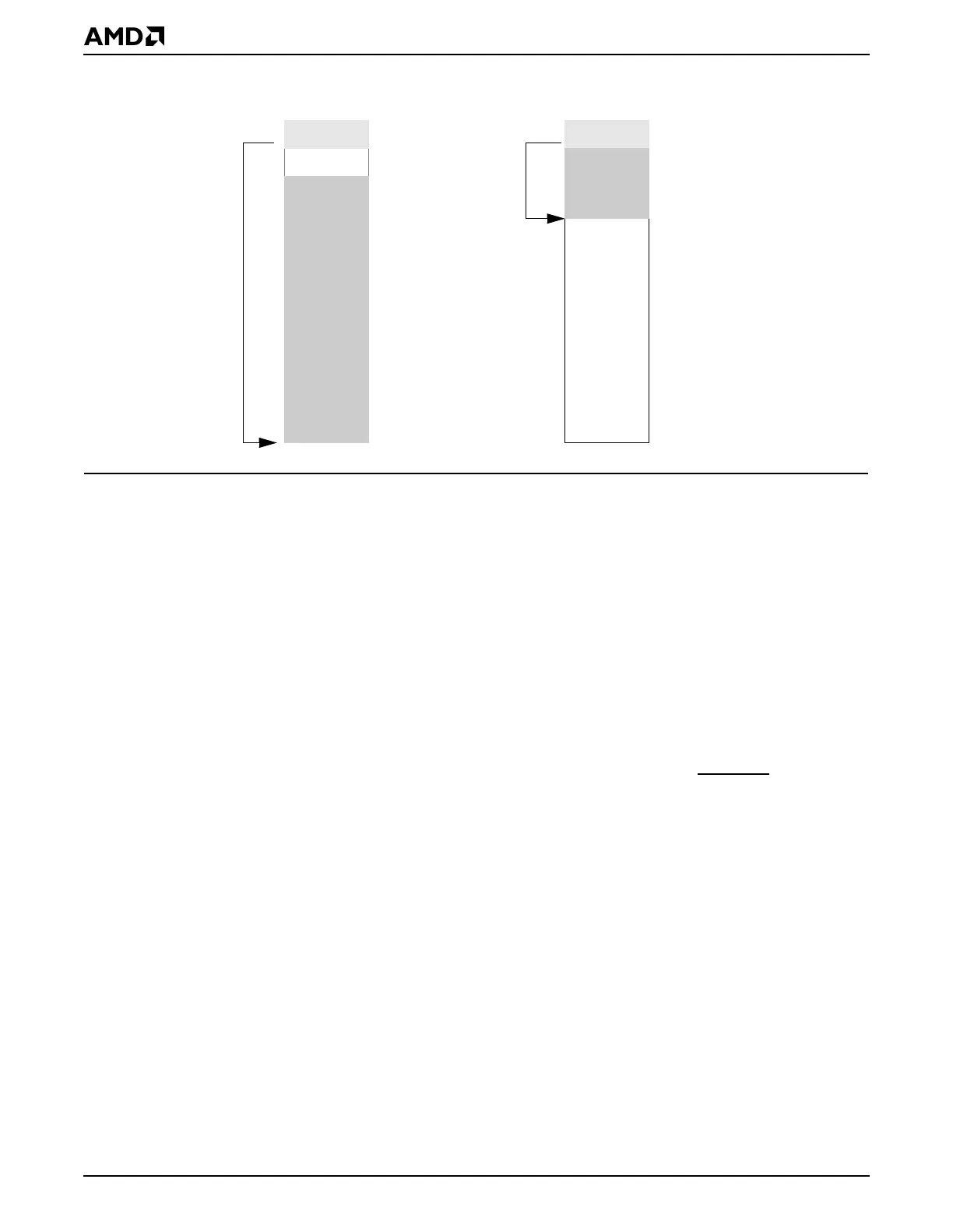

Figure 3-1 Initial Near Jump Example

The reset vector Near Jump is not required to jump to F000:0000. It can jump anywhere

into the reset segment. For example, if the reset handler code is only 16 Kbytes in size, it

could jump to F000:C000, leaving more room on the boot ROM device for other code. This

allows the reset handler to be placed right up against the reset vector, thus using the space

in the boot ROM device more efficiently.

Note: For debugging using AMDebug technology, not only should this first Jump instruction

be a Near Jump, it should be a Jump Near Indirect instruction, which is opcode FF/4. In-

circuit emulation and debug software that uses the internal trace cache searches for this

opcode to aid in determining when the reset event occurred.

As much or as little of the system initialization code can take place in the reset handler

while the system is executing from the reset segment (i.e., before the first Far Jump

instruction). For example, a native embedded system using a 32-bit only RTOS will merely

setup the protected mode data structures, switch to protected mode, and jump directly into

system boot code (the boot ROM device is the device selected by BOOTCS

).

In contrast, a system with a PC-style BIOS would initialize the SDRAM controller, shadow

the BIOS to SDRAM, and then jump to the BIOS.

3.2 CONFIGURING THE SDRAM CONTROLLER

After a system reset, the SDRAM controller configuration registers are reset to their default

states. All the SDRAM controller banks and SDRAM refresh are disabled by default. For

details on how to enable the SDRAM controller and the SDRAM configuration, see

“Initialization” on page 10-29.

Note that the ÉlanSC520 microcontroller can be reset in a manner that preserves the

operation of the SDRAM controller. This condition can be detected and handled properly

by the SDRAM initialization code.

If the Error Correction Code (ECC) logic for SDRAM is enabled, ECC operation requires

that SDRAM and its associated ECC memory be initialized. This is accomplished by the

boot code, which must write to every location in SDRAM. This process initializes the ECC

SDRAM to reflect the proper error-checking codes. If this procedure is not performed, false

F000:FFF0

F000:FFFF

F000:0000

Near

Jump

Reset Vector

Reset

Handler

F000:C000

Loading...

Loading...