System Arbitration

8-2 Élan™SC520 Microcontroller User’s Manual

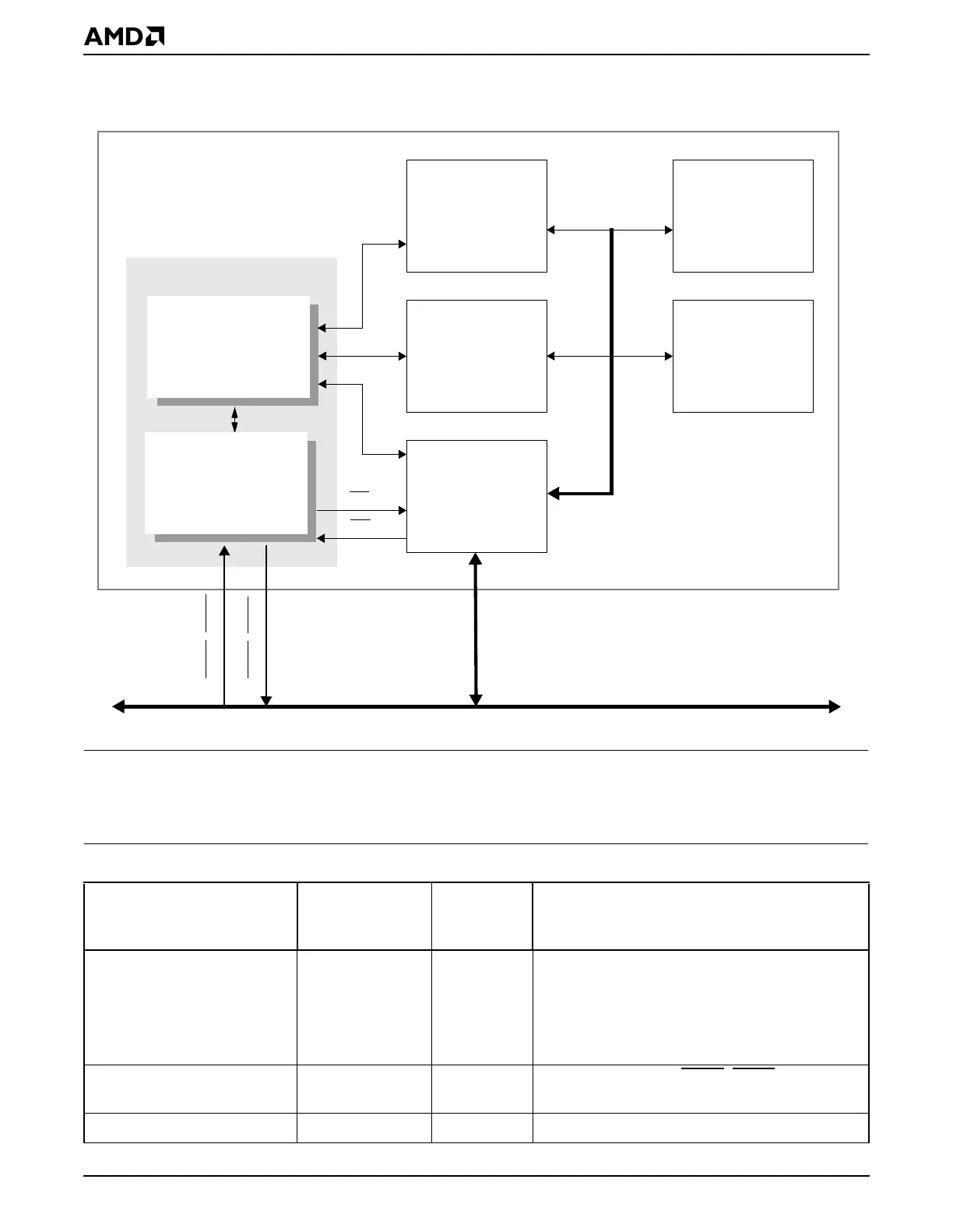

Figure 8-1 System Arbitration Block Diagram

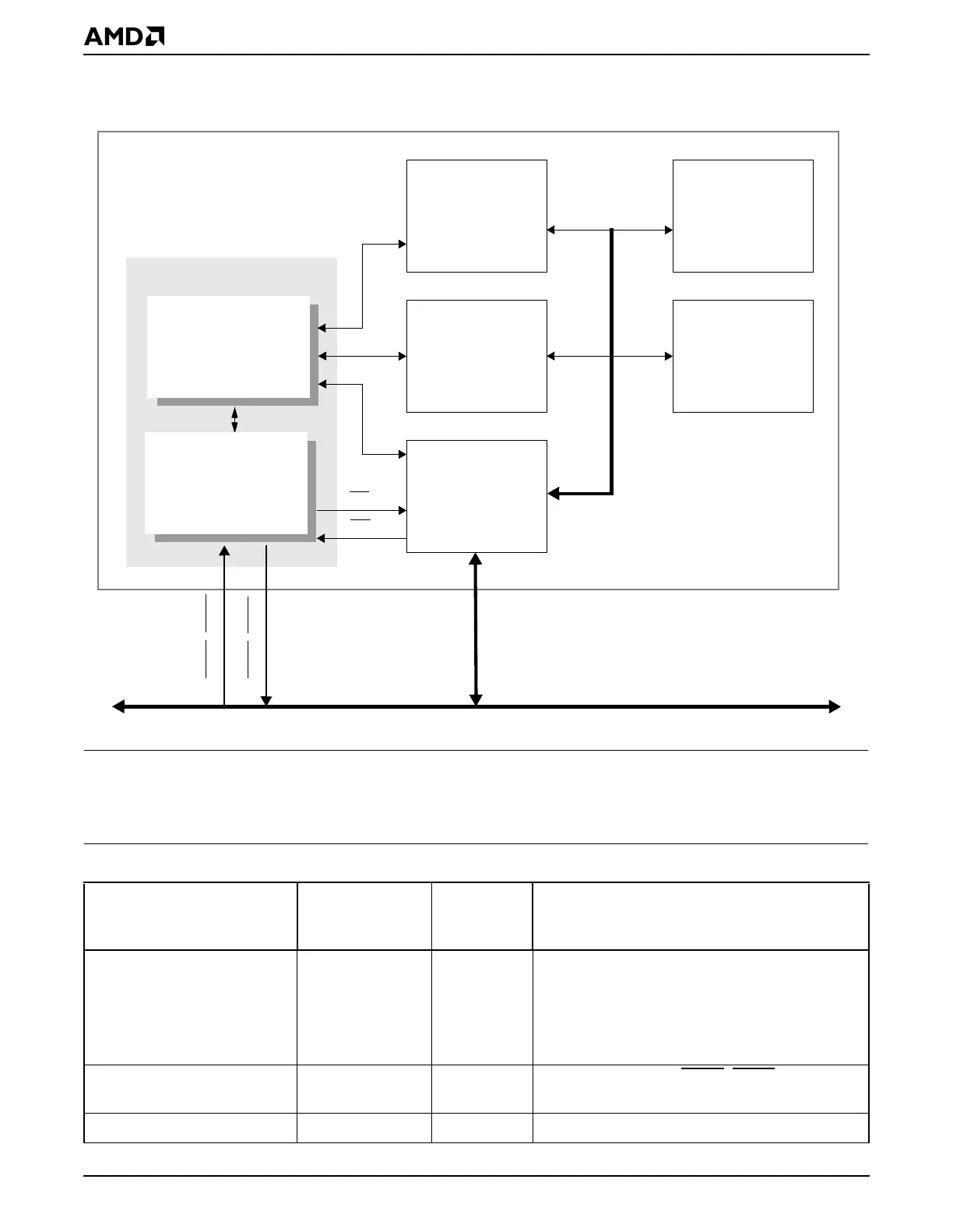

8.3 REGISTERS

The arbitration subsystem is controlled by the memory-mapped registers listed in Table 8-1.

Table 8-1 System Arbitration Registers—Memory-Mapped

Register Mnemonic

MMCR

Offset

Address Function

System Arbiter Control SYSARBCTL 70h PCI bus parking select, concurrent arbitration

mode enable, PCI bus grant time-out interrupt

enable

PCI Bus Arbiter Status PCIARBSTA 71h PCI bus arbiter grant time-out identification and

status

System Arbiter Master

Enable

SYSARBMENB 72h Enables for PCI bus REQ4

–REQ0 signals

Arbiter Priority Control ARBPRICTL 74h PCI bus arbiter rotating priority queue control

GP-DMA

PCI Host Bridge

SDRAM Controller

CPU

System Arbiter

CPU Bus

PCI Bus

GNT4–GNT0

REQ4–REQ0

req

gnt

GP Bus

ROM

Élan™SC520 Microcontroller

CPU Bus Arbiter

PCI Bus Arbiter

Loading...

Loading...