Programmable Interrupt Controller

Élan™SC520 Microcontroller User’s Manual 15-9

■ 19 are generated from internal peripheral sources, including:

– PCI host bridge/system arbiter (interrupt)

– PCI host bridge (NMI)

– SDRAM ECC single-bit error (interrupt)

– SDRAM ECC multi-bit error (NMI)

– Six timers (three GP timers and three PIT timers)

– Two UARTS

– GP-DMA buffer chaining

– SSI

– Watchdog timer

–RTC

– Write-protection violation in Programmable Address Region (PAR) register

– AMDebug interface JTAG port receive or transmit activity

– Floating point error

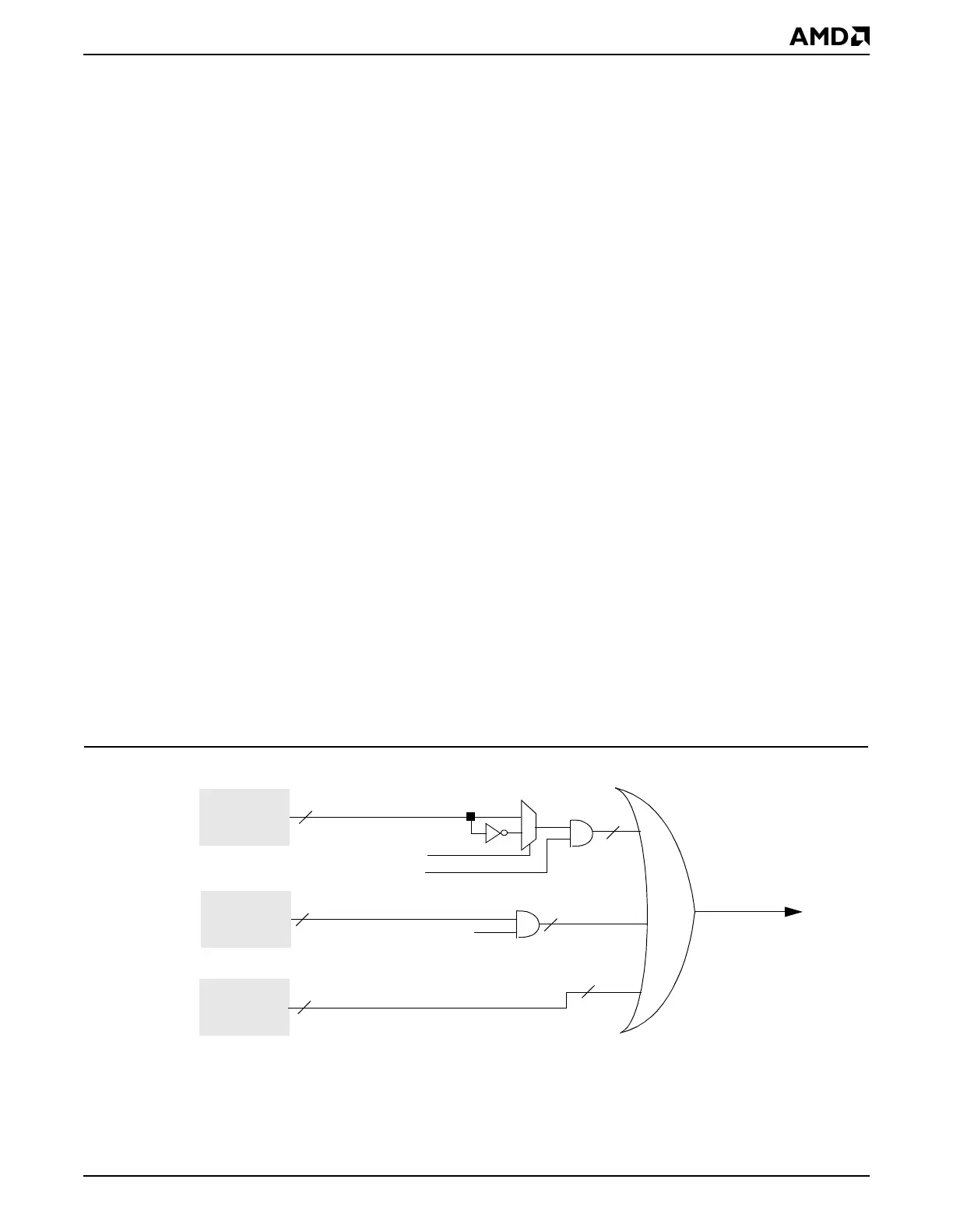

As shown in Figure 15-2 on page 15-9, of the19 internal peripheral sources:

■ 17 can be used for maskable interrupts. The two sources that cannot be configured as

a maskable interrupt are the SDRAM ECC multi-bit error NMI source and the PCI host

bridge’s separate NMI-only source.

■ 18 can be routed to the Am5

x

86 CPU’s NMI input. The only source that cannot be used

to generate an NMI is the SDRAM ECC single-bit error source.

The internal PCI host bridge and the SDRAM controller each generate a maskable interrupt

source and an NMI interrupt source. However, only the internal PCI host bridge interrupt

source can be mapped to generate either a maskable interrupt or an NMI. The SDRAM

controller’s maskable interrupt source cannot be mapped to generate an NMI.

Figure 15-2 Interrupt Sources

External

Sources

15

Internal

Sources

17 for maskable interrupt

Bits

23

0

1

polarity[0..14]

src_enb[0..14]

src_enb[15..31]

irq[1..22]_trig

15

17 (18 for NMI)

1 of 23

Control

Peripheral

To a specific controller’s

interrupt channel (x22)

or NMI

Trigger

(nmi_trig)

(18 for NMI)

(nmi_enb[15..32] for NMI)

(nmi_enb[0..14] for NMI)

Loading...

Loading...