SDRAM Controller

10-26 Élan™SC520 Microcontroller User’s Manual

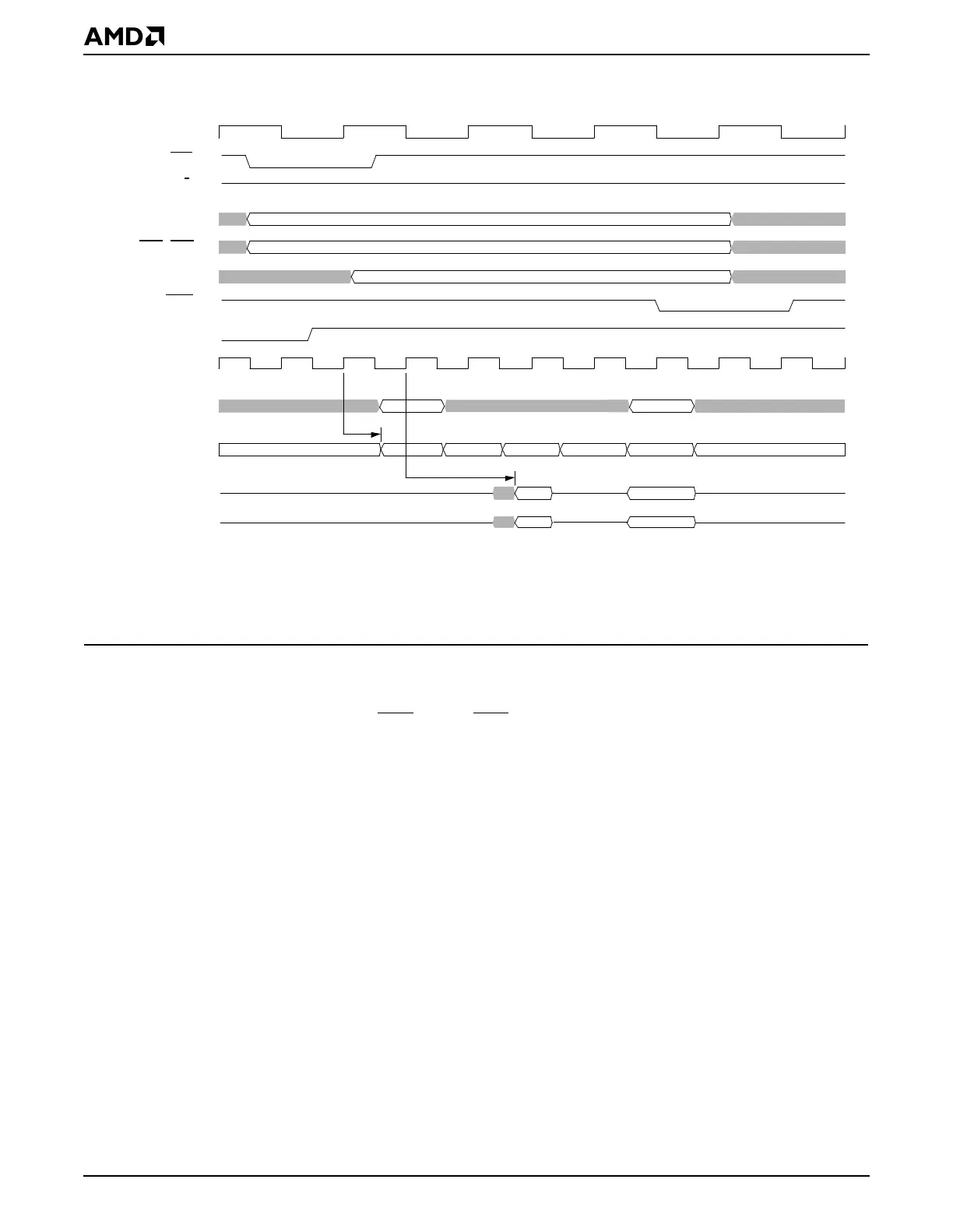

Figure 10-11 SDRAM Read-Modify-Write Cycle (for Data Write) with ECC Enabled (Page Hit)

1

Notes:

1. This timing diagram does not account for resynchronization of SDRAM signals with CLKMEMIN.

2. Contents modified with the active bytes in the write word (00AB0000).

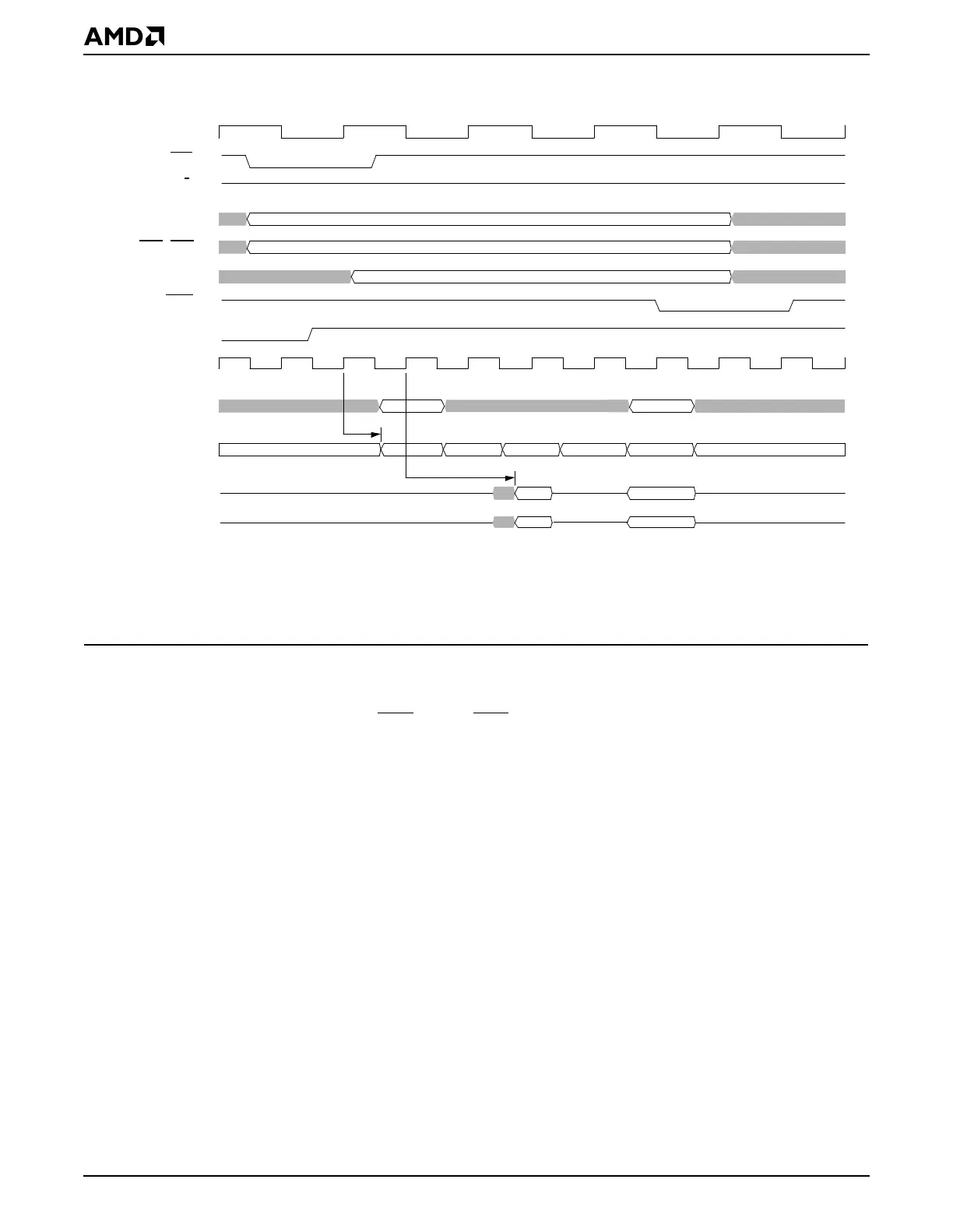

10.5.7.4 SDRAM Auto Refresh Cycle

Auto refresh, as shown in Figure 10-12, is used during normal operation of the SDRAM

and is analogous to the CAS

-before-RAS refresh in EDO DRAMs. This command is

nonpersistent, so it must be issued each time a refresh is required. The internal banks will

be precharged and idle for a minimum of the Precharge time (T

RP

) before the Auto Refresh

command is applied. When the refresh cycle has completed, all the banks of the SDRAM

will be in the precharged (idle) state. Note that this figure shows a staggered refresh cycle,

as described in “Refresh Control” on page 10-18.

The purpose of the programmable reset in the memory controller is to maintain the state

of the SDRAM during a reset. This allows SDRAM refreshes to occur during reset. See

Chapter 6, “Reset Generation”, for more information.

CAS latency = 2

00AB0000

a

1011

Rd Wr

a

2

a

clk_cpu

w/r

x5_abus

be3

–be0

x5_data_out

brdy

pghit

clk_mem

MA12–MA0,

Command

MD31–MD0

MECC6–MECC0

BA1–BA0

ads

Col

Col

Loading...

Loading...