RDMA RegistersBCM5718 Programmer’s Guide

Broadcom®

January 29, 2016 • 5718-PG108-R Page 438

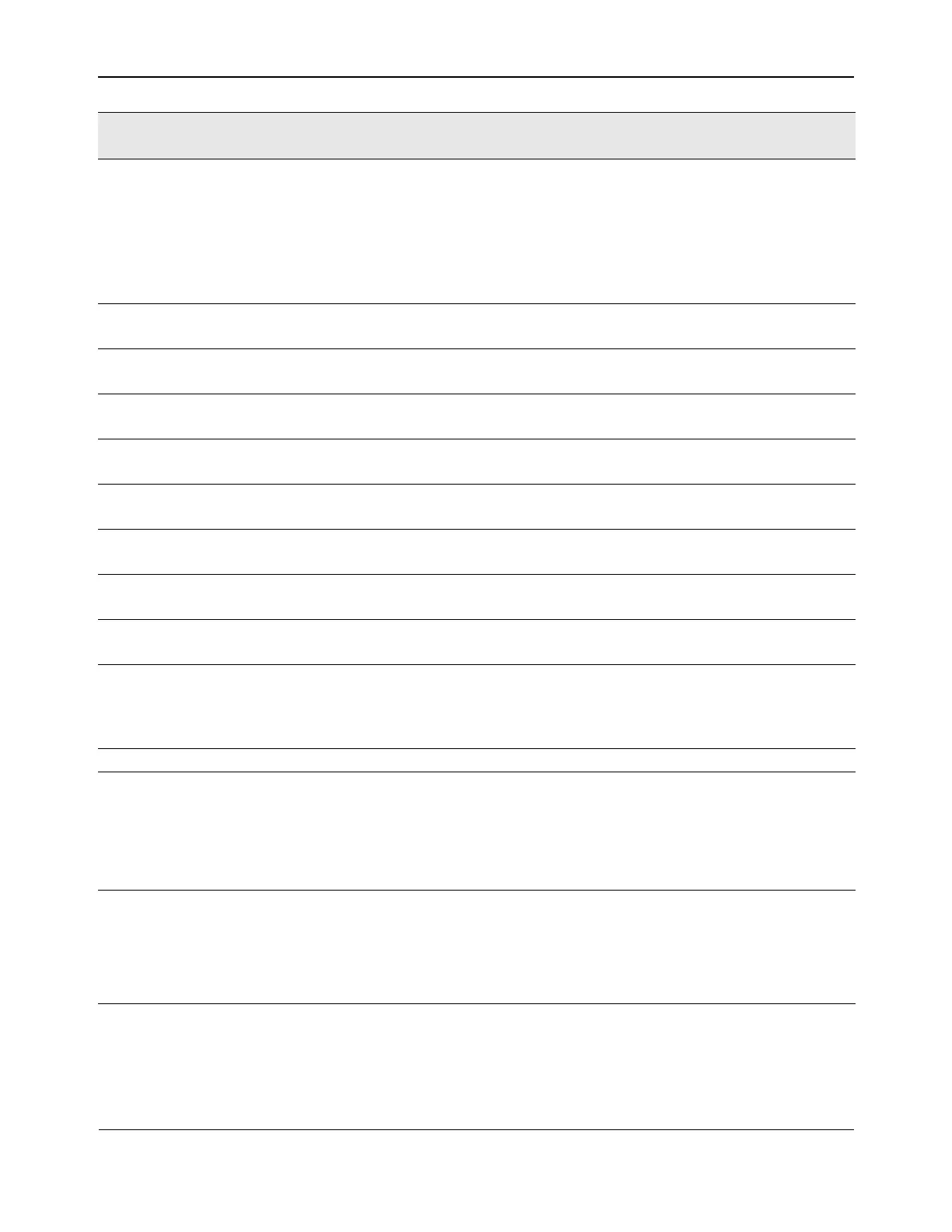

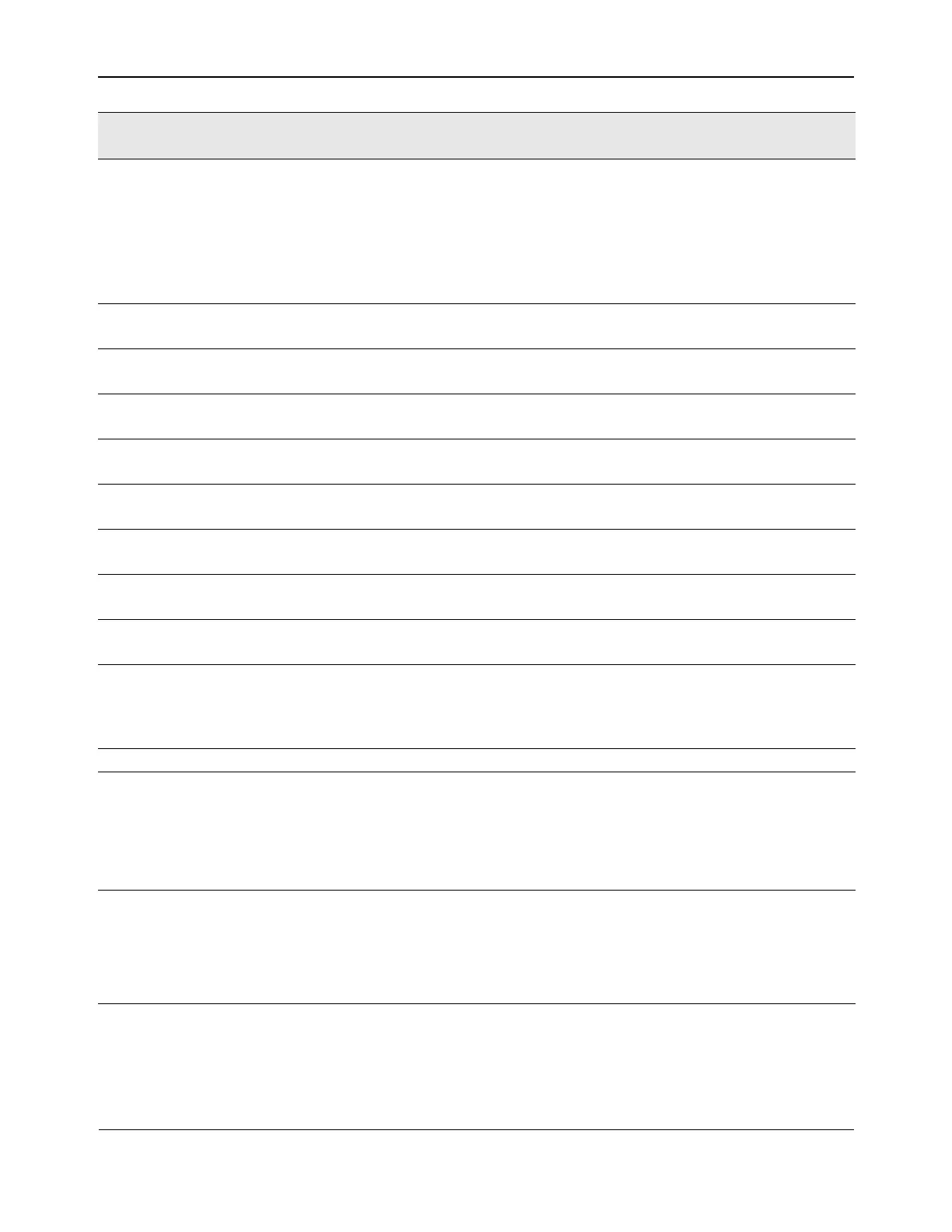

PCI Request Burst Length for

BD RDMA engine

17:16 RW 0 The two bits define the burst length that the BD

RDMA read engine would request to the PCI

block.

• 00 = 128B

• 01 = 256B

• 10 = 512B

•11 = 4KB

cq46758_fix_enable 15 RW 0 0 0: Enable fix

1: Disable fix

sbd_8b_less_fix_enable3 14 RW 0 0: Enable fix

1: Disable fix

sbd_8b_less_fix_enable2 13 RW 0 0: Enable fix

1: Disable fix

mem_too_large_fix_enable2 12 RW 0 0: Enable fix

1: Disable fix

mem_too_large_fix_enable1 11 RW 0 0: Enable fix

1: Disable fix

mem_too_large_fix_enable 10 RW 0 0: Enable fix

1: Disable fix

sbd_8b_less_fix_enable_fast_

return

9 RW 0 0: Enable fix

1: Disable fix

sbd_8b_less_fix_enable 8 RW 0 0: Enable fix

1: Disable fix

Enable hardware fix for the

wrong TCP checksum when

LSO send out

7 RW 0 The fix involves wiping out the tcp_checksum

calculation.

0: Enable Fix

1: Disable Fix

Reserved 6 RW 0 –

Fix for IP header checksum

error in high transfer rate

5 RW 0 This control bit is used to enable the fix for the IP

Header Checksum Corruption occurs when an

IPV4 payload contents match an IPV6 Header

Type.

1: Disable fix

0: enable fix

Enable hardware fix for TX

Read DMA lock-up LOCKUP

4 RW 1 Set to 1 to enable fix for clock request gap

problem of Tx Read DMA lock-up issue.

Note that increasing the ASPM L1 entry time to a

value on the order of 1ms is recommended and

may prevent this issue from occurring. See

register 0x7d28.

Name Bits Access

Default

Value

Description

Loading...

Loading...