PowerPC e500 Core Family Reference Manual, Rev. 1

4-36 Freescale Semiconductor

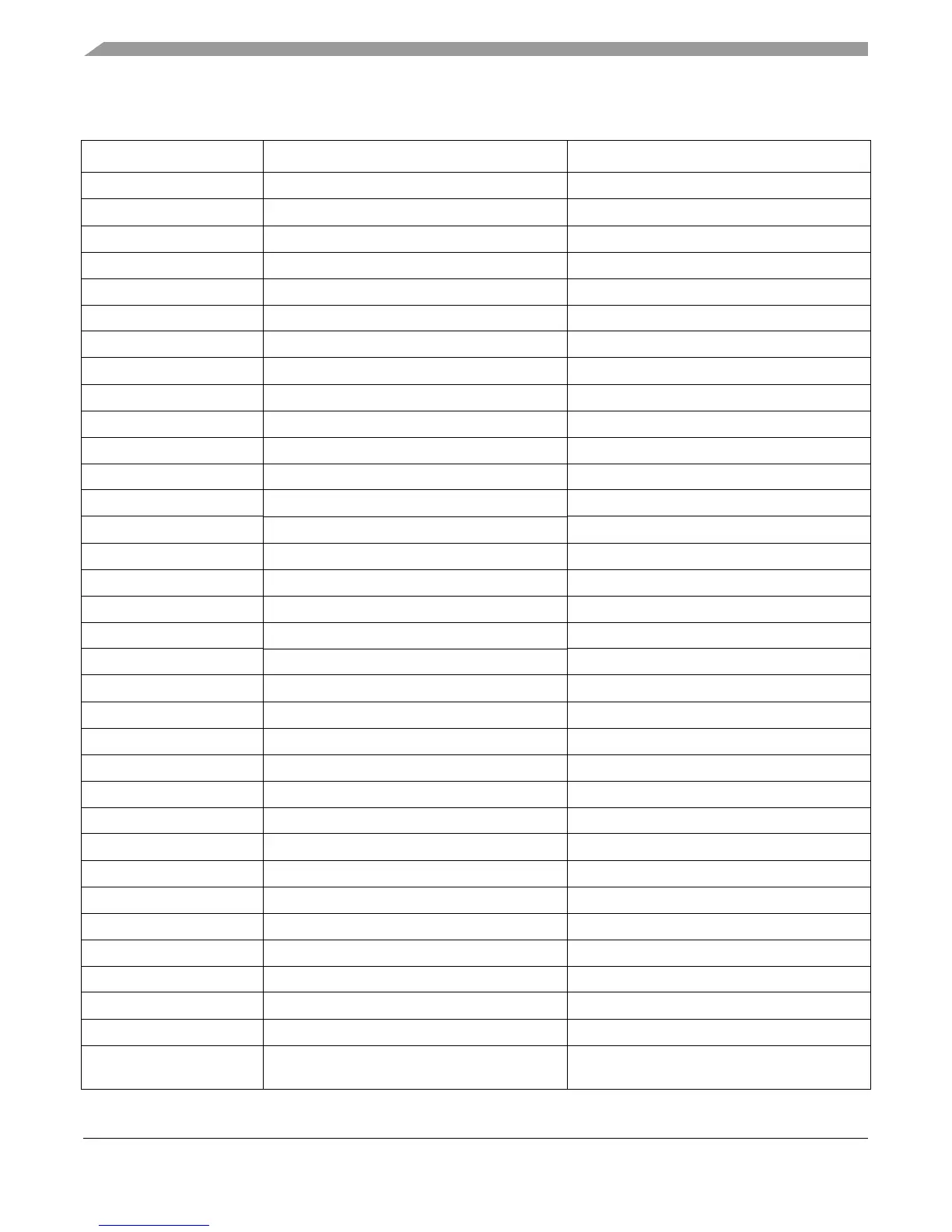

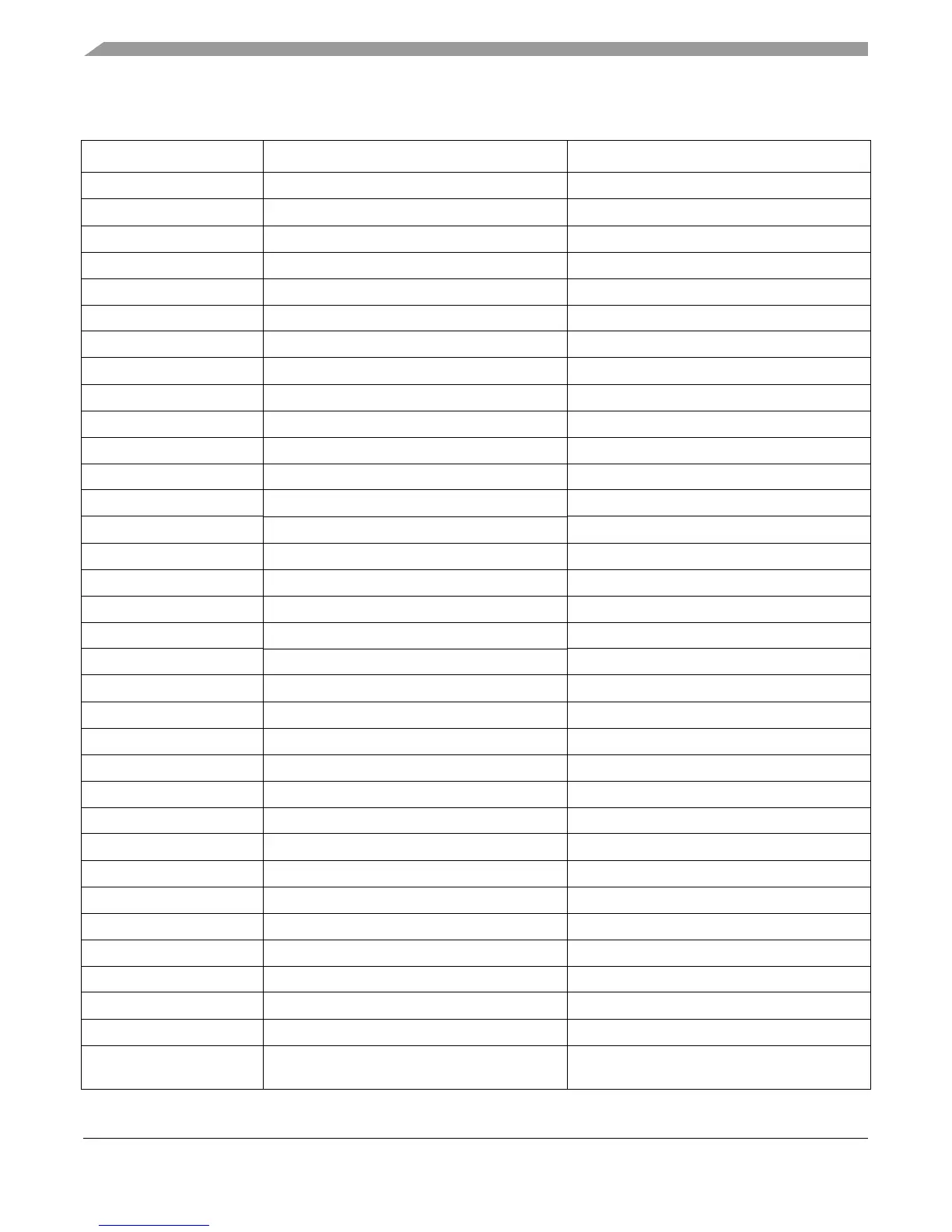

Execution Timing

evlhhesplatx 3:1 —

evlhhossplat 3:1 —

evlhhossplatx 3:1 —

evlhhousplat 3:1 —

evlhhousplatx 3:1 —

evlwhe 3:1 —

evlwhex 3:1 —

evlwhos 3:1 —

evlwhosx 3:1 —

evlwhou 3:1 —

evlwhoux 3:1 —

evlwhsplat 3:1 —

evlwhsplatx 3:1 —

evlwwsplat 3:1 —

evlwwsplatx 3:1 —

evstdd 3:1 Store

evstddx 3:1 Store

evstdh 3:1 Store

evstdhx 3:1 Store

evstdw 3:1 Store

evstdwx 3:1 Store

evstwhe 3:1 Store

evstwhex 3:1 Store

evstwho 3:1 Store

evstwhox 3:1 Store

evstwwe 3:1 Store

evstwwex 3:1 Store

evstwwo 3:1 Store

evstwwox 3:1 Store

icbi 3:1 Store

icblc 3:1 Store serialized,

icbt CT=0 0 (no-op ) —

icbt CT=1 3:1 —

icbtls Latency is long and depends on memory

latency, as well as other resource availability.

Pre- and postsync serialized.

Table 4-7. LSU Instruction Latencies (continued)

Mnemonic Cycles (Latency:Throughput)

1

Serialization

2

Loading...

Loading...