Execution Timing

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 4-37

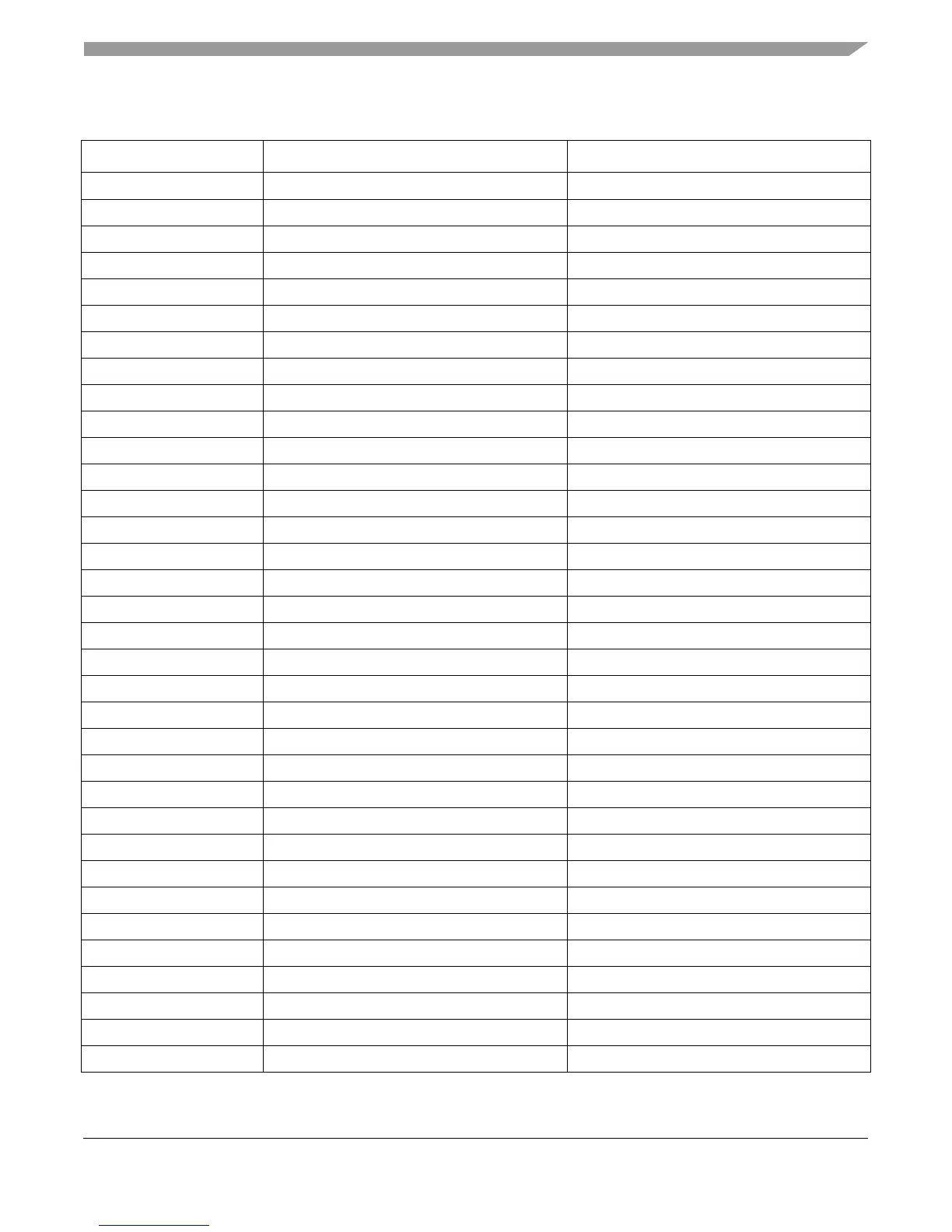

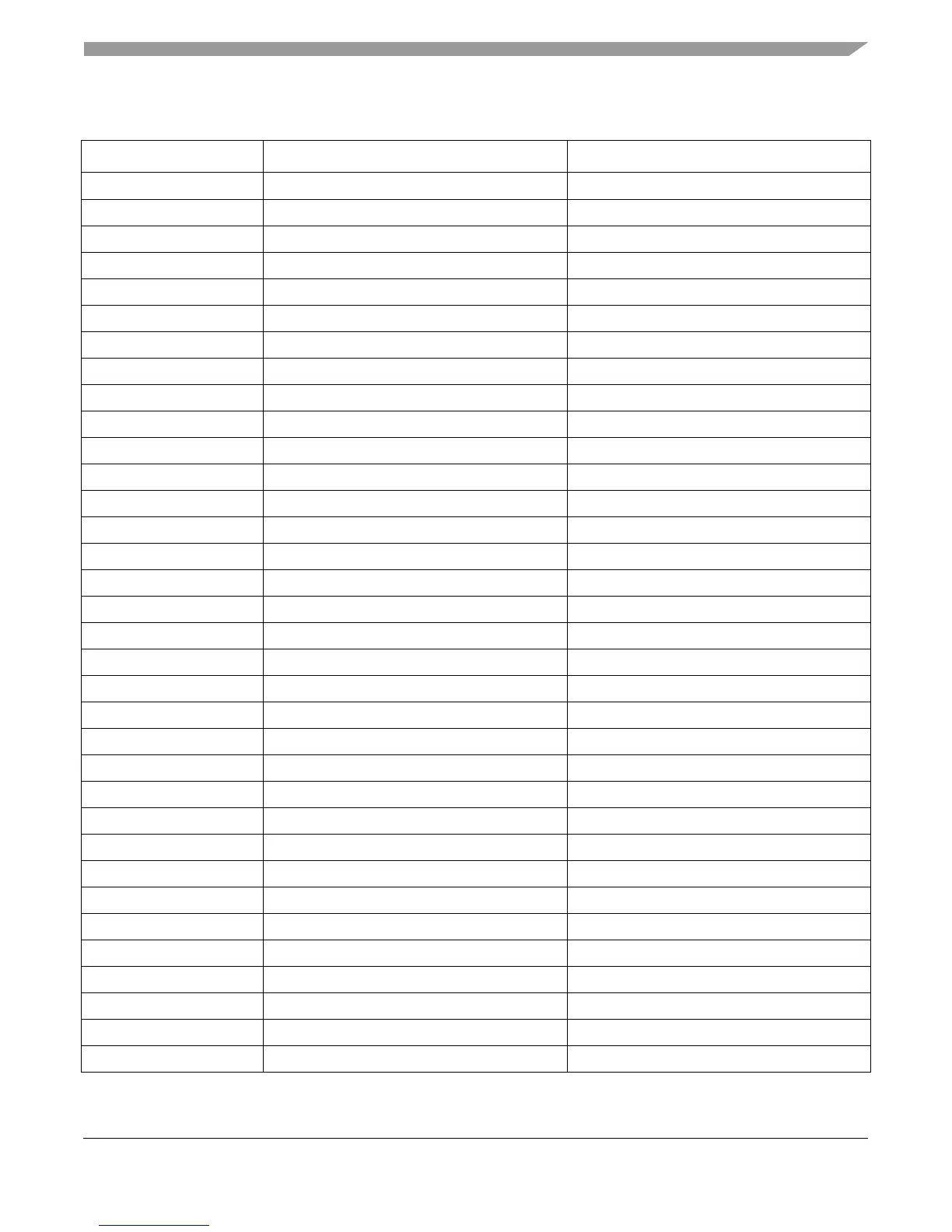

lbz 3:1 —

lbzu 3:1

3

—

lbzux 3:1

3

—

lbzx 3:1 —

lha 3:1 —

lhau 3:1

3

—

lhaux 3:1

3

—

lhax 3:1 —

lhbrx 3:1 —

lhz 3:1 —

lhzu 3:1

3

—

lhzux 3:1

3

—

lhzx 3:1 —

lmw 2 + n —

lwarx 3Presync

lwbrx 3:1 —

lwz 3:1 —

lwzu 3:1

3

—

lwzux 3:1

3

—

lwzx 3:1 —

mbar 3:1 Store serialized

msync Latency depends on bus response time. Store and postsync serialized.

stb 3:1 Store

stbu 3:1

3

Store

stbux 3:1

3

Store

stbx 3:1 Store

sth 3:1 Store

sthbrx Store

sthu 3:1

3

Store

sthux 3:1

3

Store

sthx 3:1 Store

stmw 3 + n Store

stw 3:1 Store

stwbrx 3:1 Store

Table 4-7. LSU Instruction Latencies (continued)

Mnemonic Cycles (Latency:Throughput)

1

Serialization

2

Loading...

Loading...