PowerPC e500 Core Family Reference Manual, Rev. 1

4-40 Freescale Semiconductor

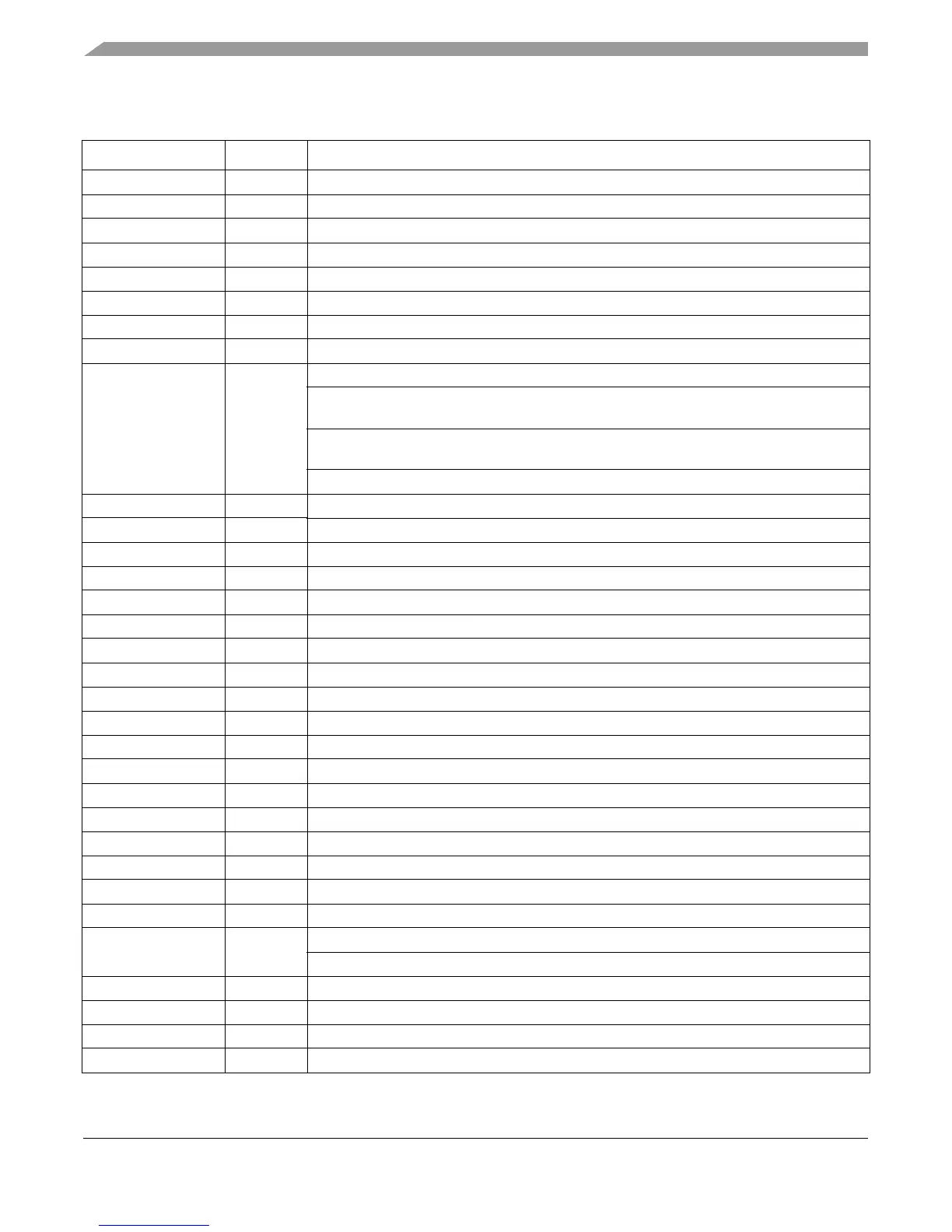

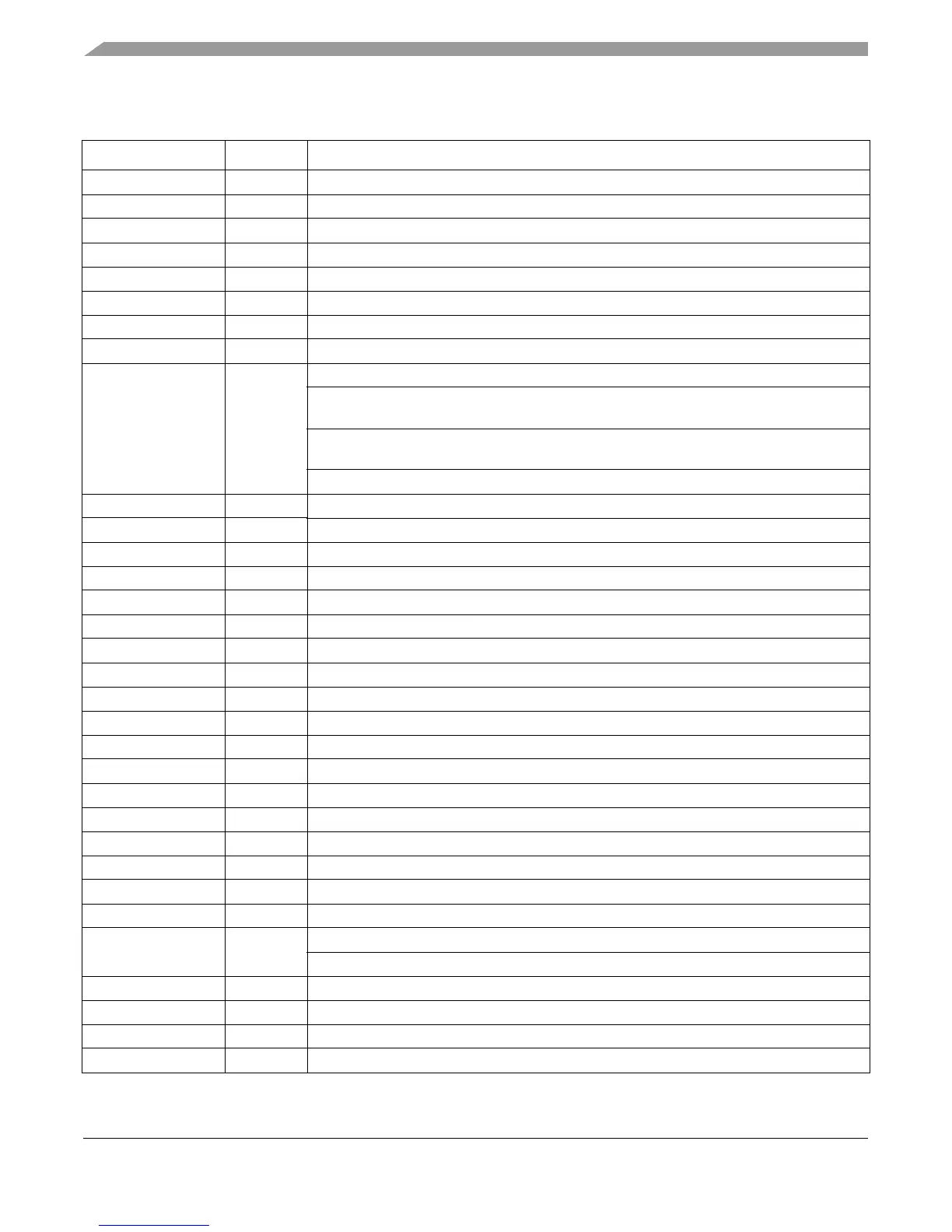

Execution Timing

evandc SU1 1

evcmpeq SU1 1

evcmpgts SU1 1

evcmpgtu SU1 1

evcmplts SU1 1

evcmpltu SU1 1

evcntlsw SU1 1

evcntlzw SU1 1

evdivws

evdivwu

MU Both the lower and upper words match the criteria described for the divw

x

4-cycle case.

1

Assuming the 4-cycle evdivw

x

case does not apply, the lower and upper words match the

criteria described for the divw

x

4- or 11-cycle case.

1

Assuming neither the 4- or 11-cycle evdivw

x

cases apply, the lower and upper words match

the criteria described for the divw

x

4-, 11-, or 19-cycle case.

1

All other cases

1

1eveqv SU1

evextsb SU1 1

evextsh SU1 1

evfsabs SU1 1

evfsadd MU 4:1

evfscfsf MU 4:1

evfscfsi MU 4:1

evfscfuf MU 4:1

evfscfui MU 4:1

evfscmpeq MU 4:1

evfscmpgt MU 4:1

evfscmplt MU 4:1

evfsctsf MU 4:1

evfsctsi MU 4:1

evfsctsiz MU 4:1

evfsctuf MU 4:1

evfsctui MU 4:1

evfsctuiz MU 4:1

evfsdiv MU 4 (if either rA or rB is 0.0)

29 (all other cases)

evfsmul MU 4:1

evfsnabs SU1 1

evfsneg SU1 1

evfssub MU 4:1

Table 4-8. SPE and Embedded Floating-Point APU Instruction Latencies (continued)

Mnemonic Unit Cycles (Latency:Throughput)

Loading...

Loading...