Auxiliary Processing Units (APUs)

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 10-9

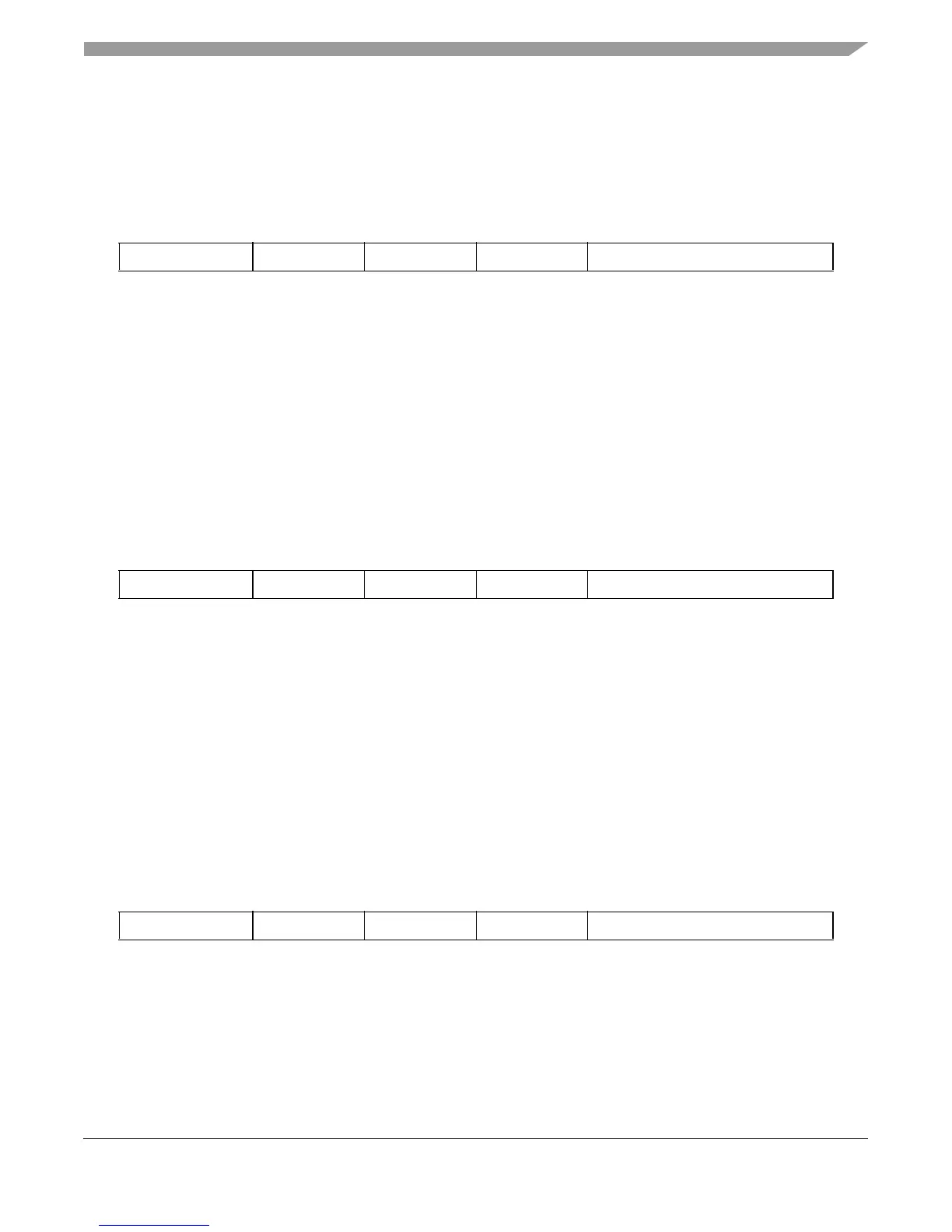

efdcfsf efdcfsf

Convert Floating-Point Double-Precision from Signed Fraction

efdcfsf rD,rB

rD

0:63

← CnvtI32ToFP64(rB

32:63

, SIGN, F)

The signed fractional low element in rB is converted to a double-precision floating-point value

using the current rounding mode and the result is placed into rD.

Exceptions: None

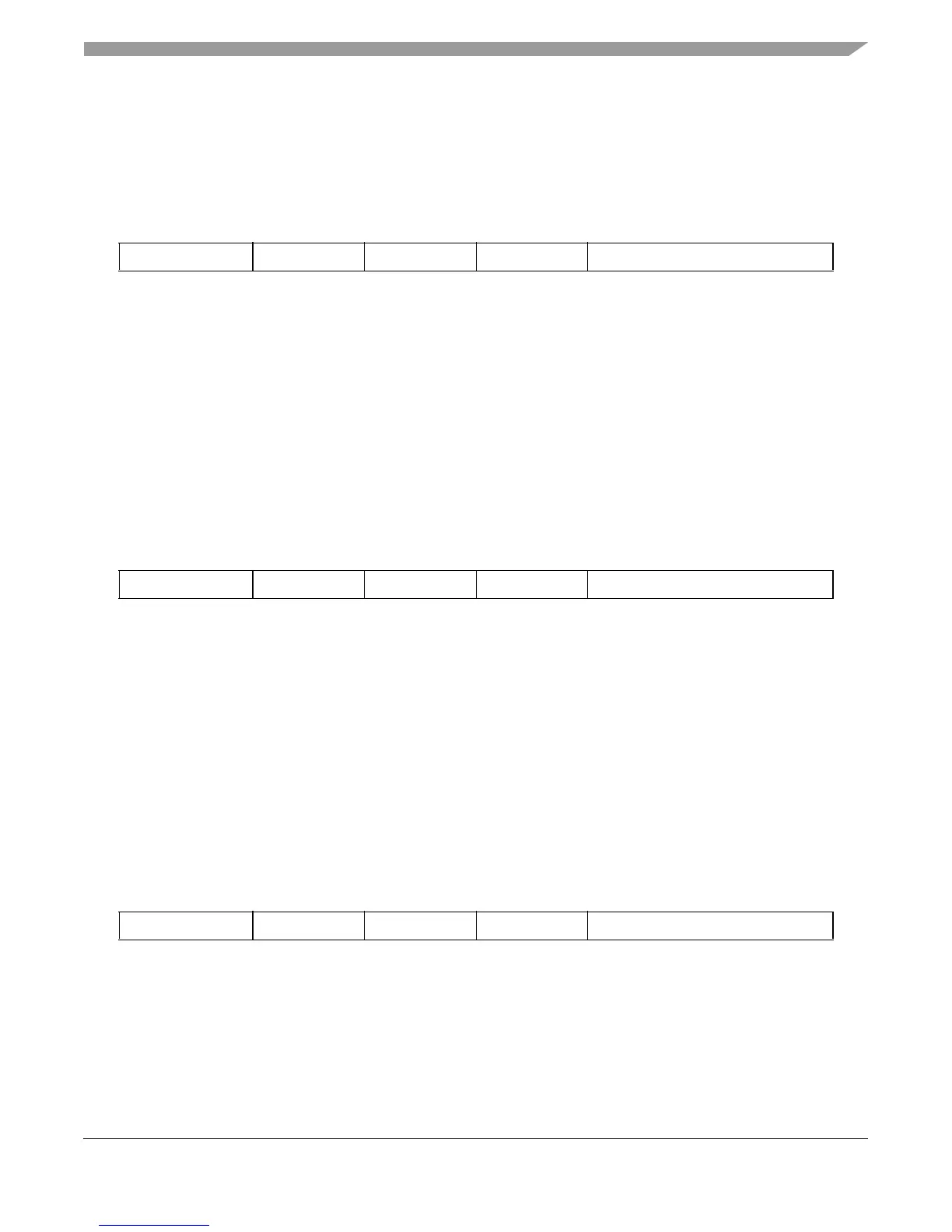

efdcfsi efdcfsi

Convert Floating-Point Double-Precision from Signed Integer

efdcfsi rD,rB

rD

0:63

← CnvtSI32ToFP64(rB

32:63

, SIGN, I)

The signed integer low element in rB is converted to a double-precision floating-point value using

the current rounding mode and the result is placed into rD.

Exceptions: None

efdcfuf efdcfuf

Convert Floating-Point Double-Precision from Unsigned Fraction

efdcfuf rD,rB

rD

0:63

← CnvtI32ToFP64(rB

32:63

, UNSIGN, F)

The unsigned fractional low element in rB is converted to a double-precision floating-point value

using the current rounding mode and the result is placed into rD.

Exceptions: None

0 56 101115162021 31

000100 rD 00000 rB 0 1011110011

0 56 101115162021 31

000100 rD 00000 rB 0 1011110001

0 56 101115162021 31

000100 rD 00000 rB 0 1011110010

Loading...

Loading...