PowerPC e500 Core Family Reference Manual, Rev. 1

10-10 Freescale Semiconductor

Auxiliary Processing Units (APUs)

efdcfui efdcfui

Convert Floating-Point Double-Precision from Unsigned Integer

efdcfui rD,rB

rD

0:63

← CnvtSI32ToFP64(rB

32:63

, UNSIGN, I)

The unsigned integer low element in rB is converted to a double-precision floating-point value

using the current rounding mode and the result is placed into rD.

Exceptions: None

efdcmpeq efdcmpeq

Floating-Point Double-Precision Compare Equal

efdcmpeq crfD,rA,rB

al ← rA

0:63

bl ← rB

0:63

if (al = bl) then cl ← 1

else cl ← 0

CR

4*crD:4*crD+3

← undefined || cl || undefined || undefined

rA is compared against rB. If rA is equal to rB, the bit in the crfD is set, otherwise it is cleared.

Comparison ignores the sign of 0 (+0 = -0).

Exceptions:

If the contents of rA or rB are Infinity, Denorm, or NaN, SPEFSCR[FINV] is set, and the FGH

FXH, FG and FX bits are cleared. If floating-point invalid input exceptions are enabled, an

interrupt is taken and the condition register is not updated. Otherwise, the comparison proceeds

after treating NaNs, Infinities, and Denorms as normalized numbers, using their values of ‘e’ and

‘f’ directly.

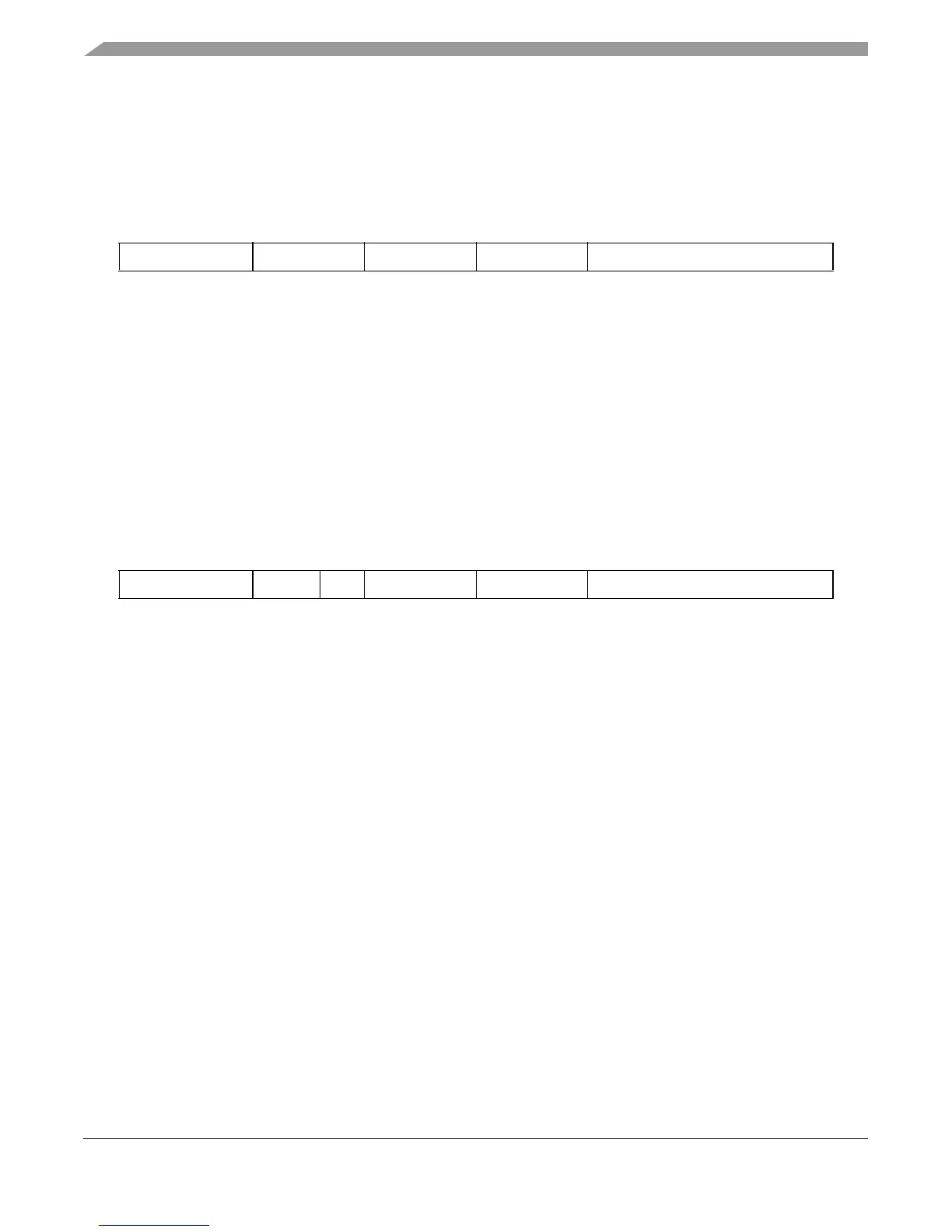

0 56 101115162021 31

000100 rD 00000 rB 0 1011110000

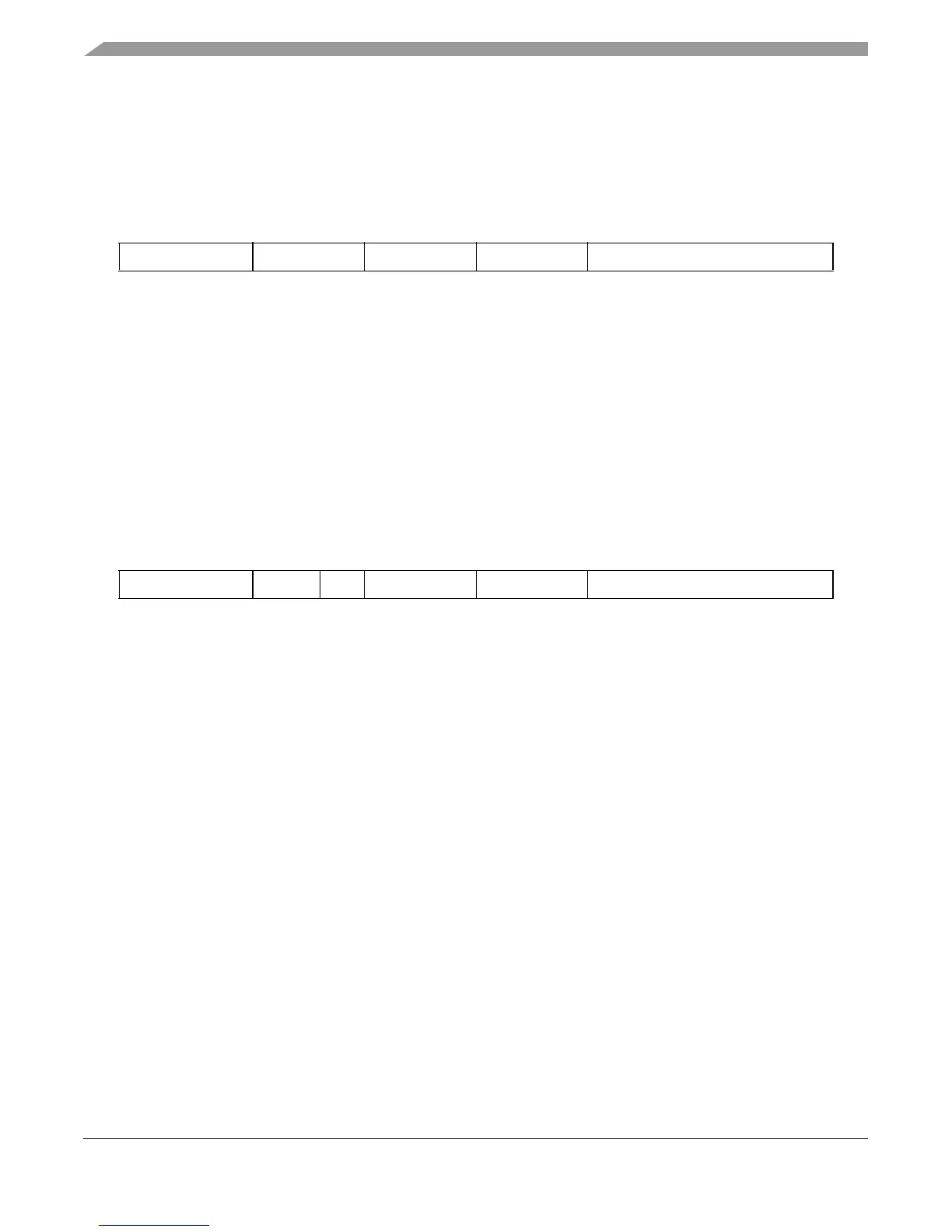

0 5689101115162021 31

000100 crfD00 rA rB 0 1011101110

Loading...

Loading...