PowerPC e500 Core Family Reference Manual, Rev. 1

10-12 Freescale Semiconductor

Auxiliary Processing Units (APUs)

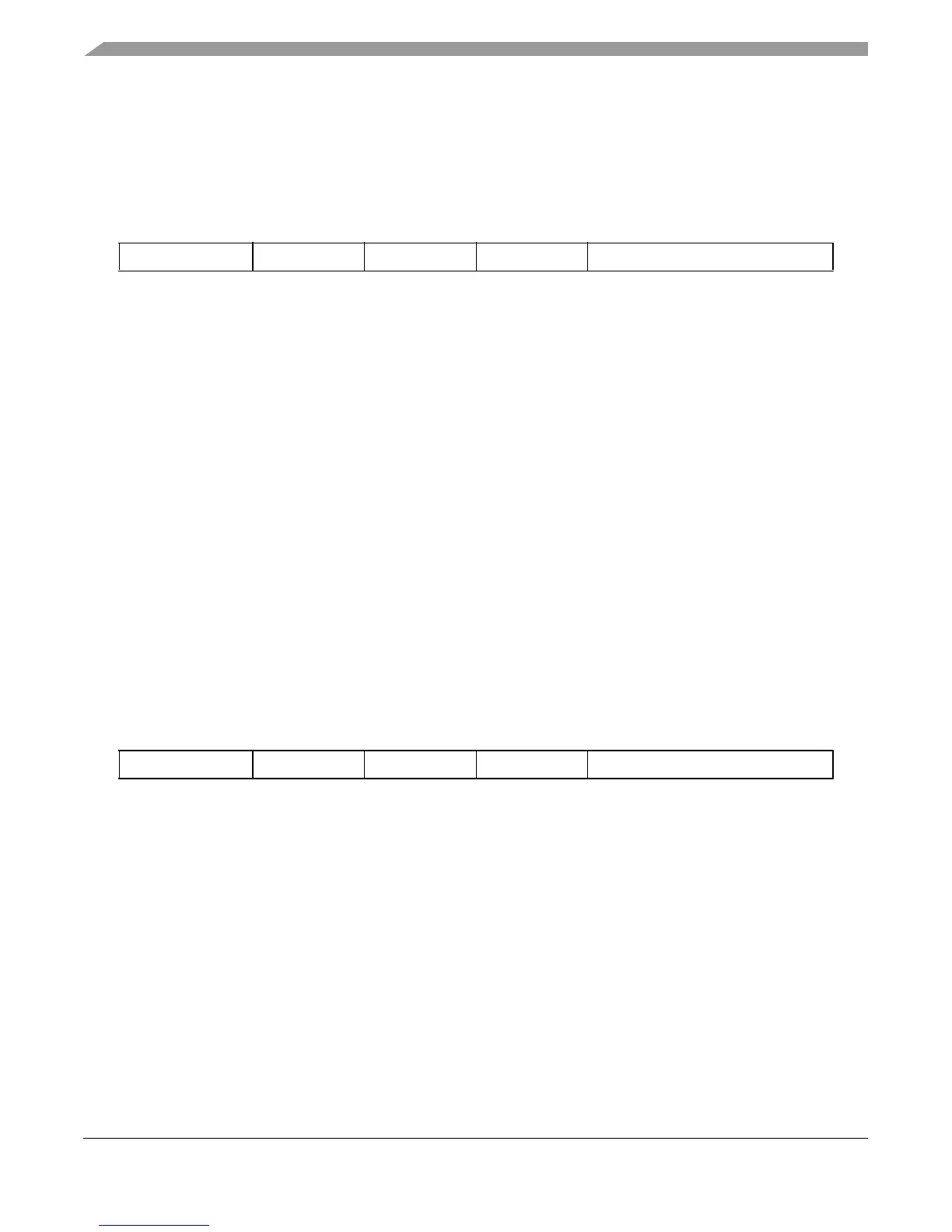

efdctsf efdctsf

Convert Floating-Point Double-Precision to Signed Fraction

efdctsf rD,rB

rD

32:63

← CnvtFP64ToI32Sat(rB

0:63

, SIGN, ROUND, F)

The double-precision floating-point value in rB is converted to a signed fraction using the current

rounding mode and the result is saturated if it cannot be represented in a 32-bit fraction. NaNs are

converted as though they were zero.

Exceptions:

If the rB contents are Infinity, Denorm, or NaN, or if an overflow occurs, SPEFSCR[FINV] is set

and FG and FX are cleared. If SPEFSCR[FINVE] is set, an interrupt is taken and rD is not

updated.

If conversion is inexact, inexact status is signalled and SPEFSCR[FINXS] is set. If the

floating-point inexact exception is enabled, a floating-point round interrupt is taken, rD is updated

with the truncated result, and FG and FX are updated so the handler can perform rounding.

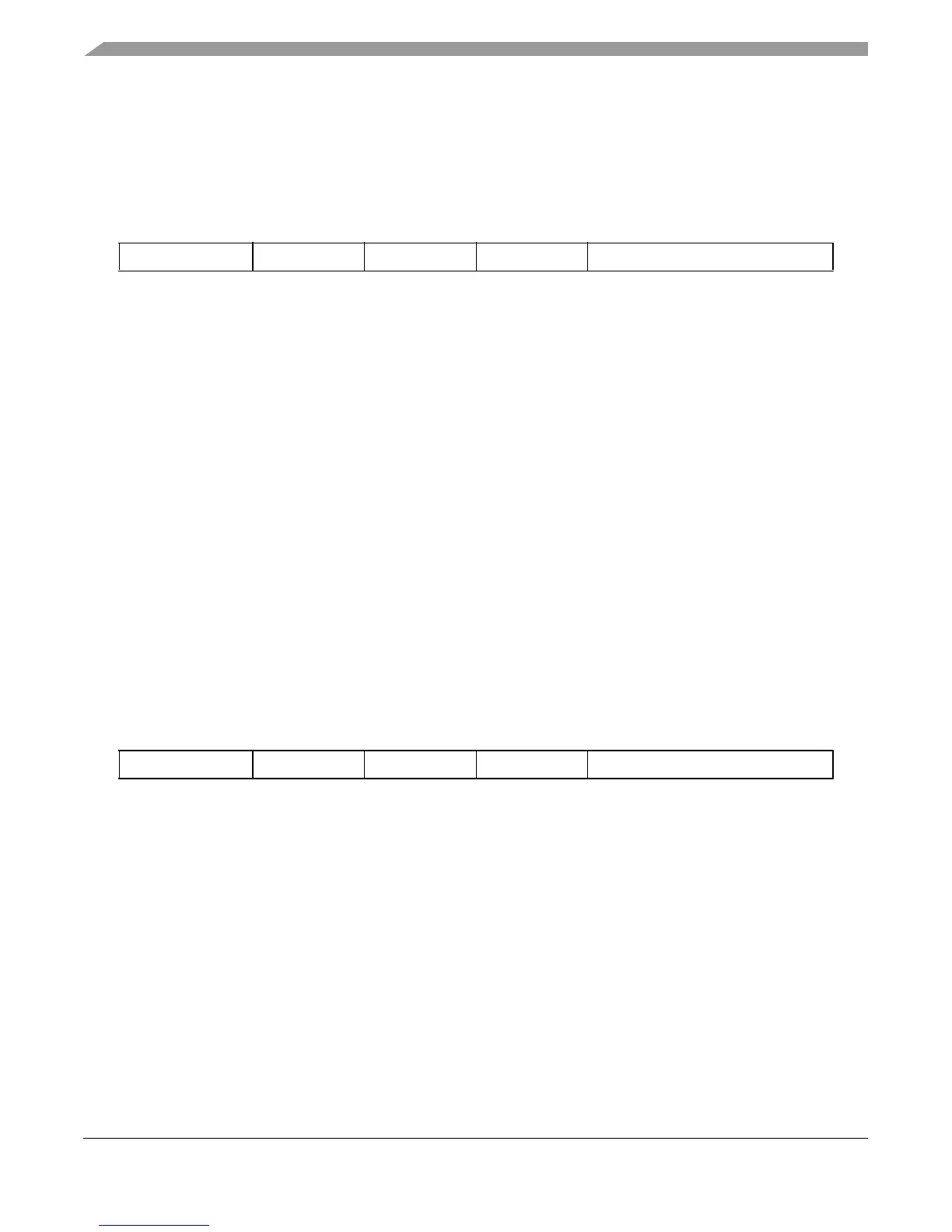

efdctsi efdctsi

Convert Floating-Point Double-Precision to Signed Integer

efdctsi rD,rB

rD

32:63

← CnvtFP64ToI32Sat(rB

0:63

, SIGN, ROUND, I)

The double-precision floating-point value in rB is converted to a signed integer using the current

rounding mode and the result is saturated if it cannot be represented in a 32-bit integer. NaNs are

converted as though they were zero.

Exceptions:

If rB contents are Infinity, Denorm, or NaN or if an overflow occurs, SPEFSCR[FINV] is set and

FG and FX are cleared. If SPEFSCR[FINVE] is set, an interrupt is taken, rD is not updated, and

no other status bits are set.

If conversion is inexact, inexact status is signalled and SPEFSCR[FINXS] is set. If the

floating-point inexact exception is enabled, a floating-point round interrupt is taken, rD is updated

with the truncated result, and FG and FX are updated so the handler can perform rounding.

0 56 101115162021 31

000100 rD 00000 rB 0 1011110111

0 56 101115162021 31

000100 rD 00000 rB 0 1011110101

Loading...

Loading...