Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1038/1096 Doc ID 13902 Rev 12

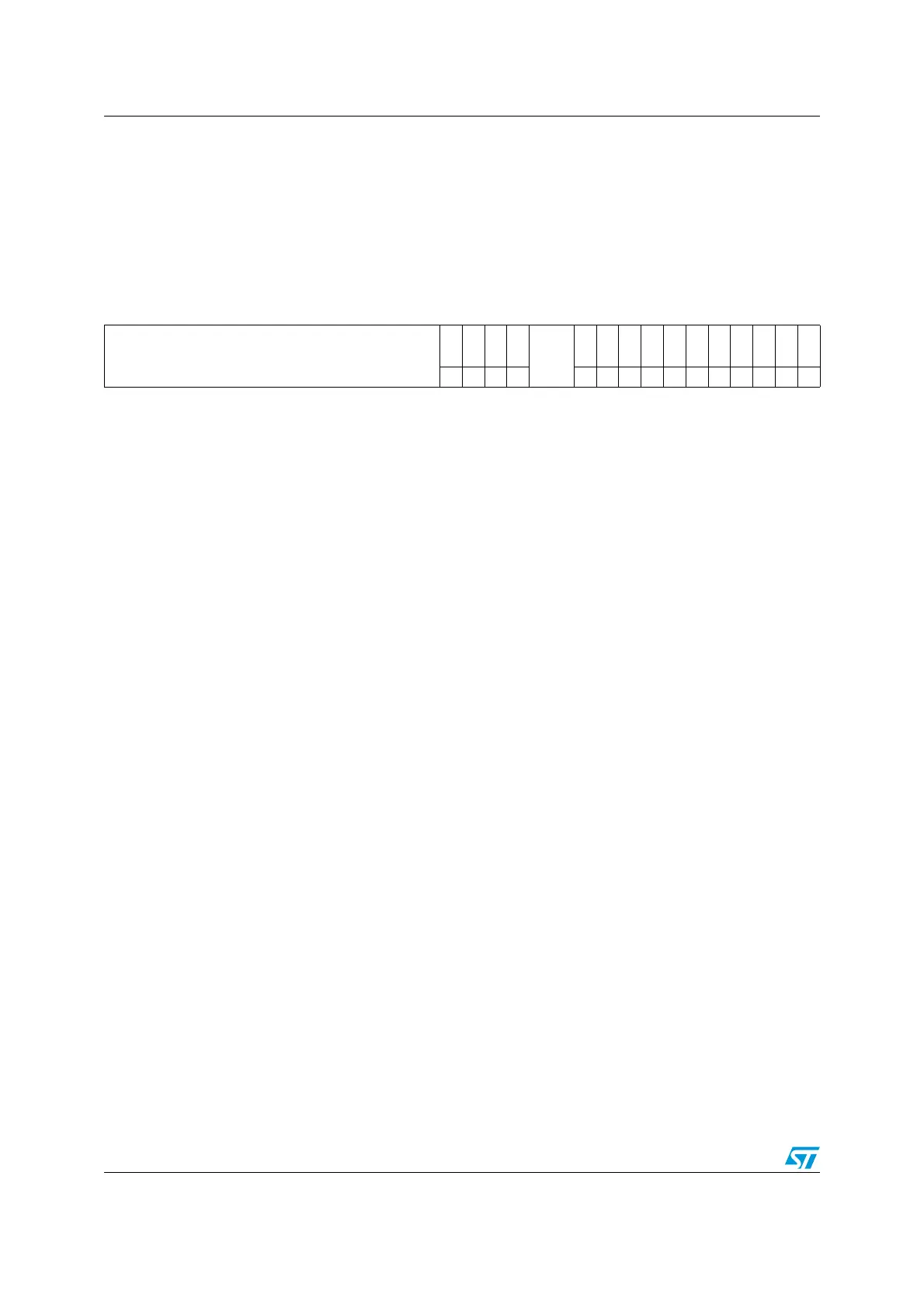

Ethernet DMA interrupt enable register (ETH_DMAIER)

Address offset: 0x101C

Reset value: 0x0000 0000

The Interrupt enable register enables the interrupts reported by ETH_DMASR. Setting a bit

to 1 enables a corresponding interrupt. After a hardware or software reset, all interrupts are

disabled.

313029282726252423222120191817161514131211109876543210

Reserved

NISE

AISE

ERIE

FBEIE

Reserved

ETIE

RWTIE

RPSIE

RBUIE

RIE

TUIE

ROIE

TJTIE

TBUIE

TPSIE

TIE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:17 Reserved

Bit 16 NISE: Normal interrupt summary enable

When this bit is set, a normal interrupt is enabled. When this bit is cleared, a normal interrupt

is disabled. This bit enables the following bits:

– ETH_DMASR [0]: Transmit Interrupt

– ETH_DMASR [2]: Transmit buffer unavailable

– ETH_DMASR [6]: Receive interrupt

– ETH_DMASR [14]: Early receive interrupt

Bit 15 AISE: Abnormal interrupt summary enable

When this bit is set, an abnormal interrupt is enabled. When this bit is cleared, an abnormal

interrupt is disabled. This bit enables the following bits:

– ETH_DMASR [1]: Transmit process stopped

– ETH_DMASR [3]: Transmit jabber timeout

– ETH_DMASR [4]: Receive overflow

– ETH_DMASR [5]: Transmit underflow

– ETH_DMASR [7]: Receive buffer unavailable

– ETH_DMASR [8]: Receive process stopped

– ETH_DMASR [9]: Receive watchdog timeout

– ETH_DMASR [10]: Early transmit interrupt

– ETH_DMASR [13]: Fatal bus error

Bit 14 ERIE: Early receive interrupt enable

When this bit is set with the normal interrupt summary enable bit (ETH_DMAIER register[16]),

the early receive interrupt is enabled.

When this bit is cleared, the early receive interrupt is disabled.

Bit 13 FBEIE: Fatal bus error interrupt enable

When this bit is set with the abnormal interrupt summary enable bit (ETH_DMAIER

register[15]), the fatal bus error interrupt is enabled.

When this bit is cleared, the fatal bus error enable interrupt is disabled.

Bits 12:11 Reserved

Bit 10 ETIE: Early transmit interrupt enable

When this bit is set with the abnormal interrupt summary enable bit (ETH_DMAIER register

[15]), the early transmit interrupt is enabled.

When this bit is cleared, the early transmit interrupt is disabled.

Loading...

Loading...