RM0008 Connectivity line devices: reset and clock control (RCC)

Doc ID 13902 Rev 12 141/1096

8.3.6 AHB Peripheral Clock enable register (RCC_AHBENR)

Address offset: 0x14

Reset value: 0x0000 0014

Access: no wait state, word, half-word and byte access

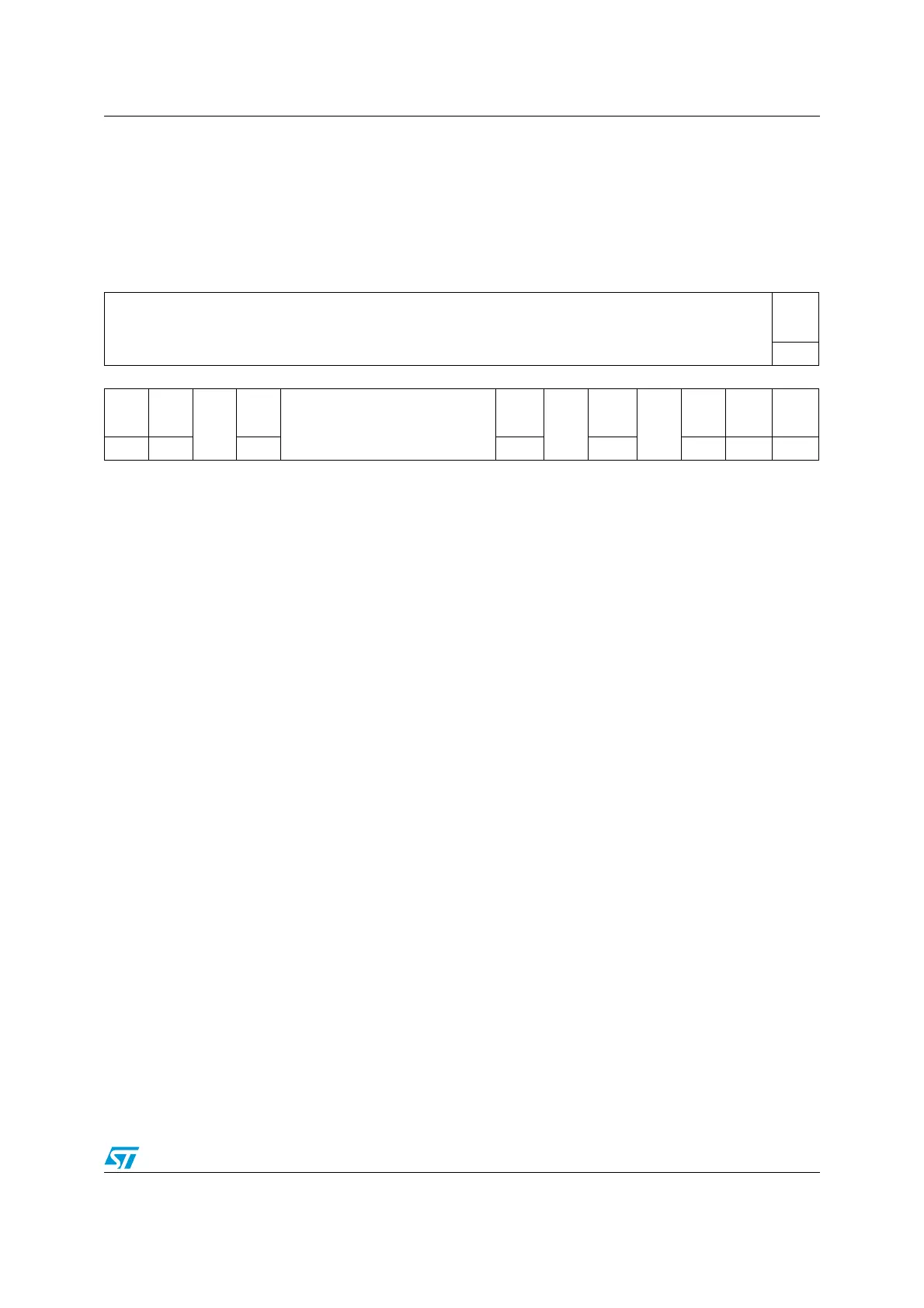

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

ETH

MACR

XEN

rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ETHM

ACTX

EN

ETHM

ACEN

Res.

OTGF

SEN

Reserved

CRCEN

Res.

FLITFE

N

Res.

SRAM

EN

DMA2

EN

DMA1

EN

rw rw rw rw rw rw rw rw

Bits 31:17 Reserved, always read as 0.

Bit 16 ETHMACRXEN: Ethernet MAC RX clock enable

Set and cleared by software.

0: Ethernet MAC RX clock disabled

1: Ethernet MAC RX clock enabled

Note: In the RMII mode, if this clock is enabled, the RMII clock of the MAC is also enabled.

Bit 15 ETHMACTXEN: Ethernet MAC TX clock enable

Set and cleared by software.

0: Ethernet MAC TX clock disabled

1: Ethernet MAC TX clock enabled

Note: In the RMII mode, if this clock is enabled, the RMII clock of the MAC is also enabled.

Bit 14 ETHMACEN: Ethernet MAC clock enable

Set and cleared by software. Selection of PHY interface (MII/RMII) must be done before

enabling the MAC clock.

0: Ethernet MAC clock disabled

1: Ethernet MAC clock enabled

Bit 13 Reserved, always read as 0.

Bit 12 OTGFSEN: USB OTG FS clock enable

Set and cleared by software.

0: USB OTG FS clock disabled

1: USB OTG FS clock enabled

Bits 11:7 Reserved, always read as 0.

Bit 6 CRCEN: CRC clock enable

Set and cleared by software.

0: CRC clock disabled

1: CRC clock enabled

Bit 5 Reserved, always read as 0.

Loading...

Loading...