Inter-integrated circuit (I

2

C) interface RM0008

746/1096 Doc ID 13902 Rev 12

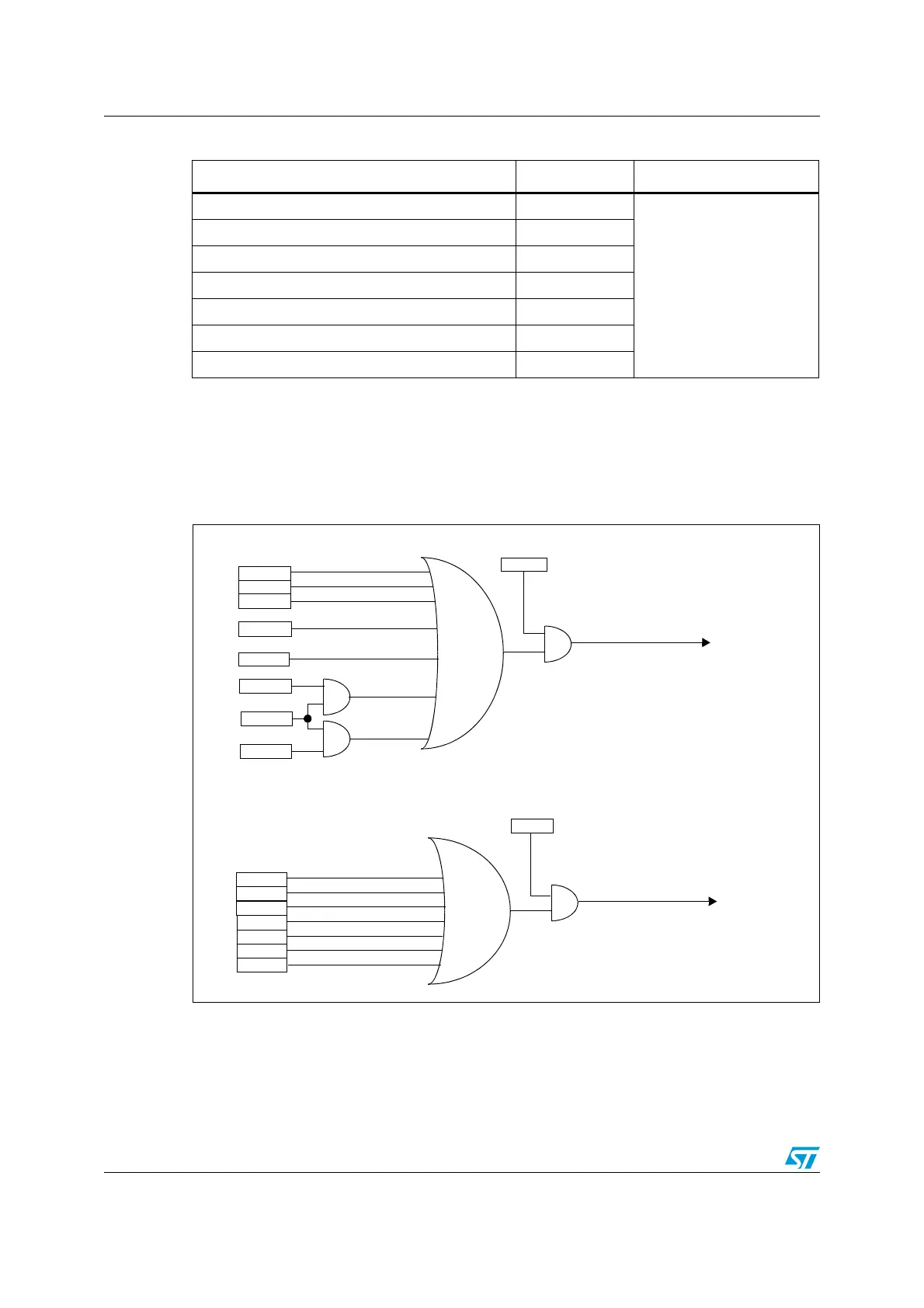

Note: 1 SB, ADDR, ADD10, STOPF, BTF, RxNE and TxE are logically ORed on the same interrupt

channel.

2 BERR, ARLO, AF, OVR, PECERR, TIMEOUT and SMBALERT are logically ORed on the

same interrupt channel.

Figure 277. I

2

C interrupt mapping diagram

Bus error BERR

ITERREN

Arbitration loss (Master) ARLO

Acknowledge failure AF

Overrun/Underrun OVR

PEC error PECERR

Timeout/Tlow error TIMEOUT

SMBus Alert SMBALERT

Table 188. I

2

C Interrupt requests (continued)

Interrupt event Event flag Enable control bit

ADDR

SB

ADD10

RxNE

TxE

BTF

it_event

ARLO

BERR

AF

OVR

PECERR

TIMEOUT

SMBALERT

ITERREN

it_error

ITEVFEN

ITBUFEN

STOPF

Loading...

Loading...