Flexible static memory controller (FSMC) RM0008

506/1096 Doc ID 13902 Rev 12

Note: The FSMC_BWTRx register is valid only if extended mode is set (mode B), otherwise all its

content is don’t care.

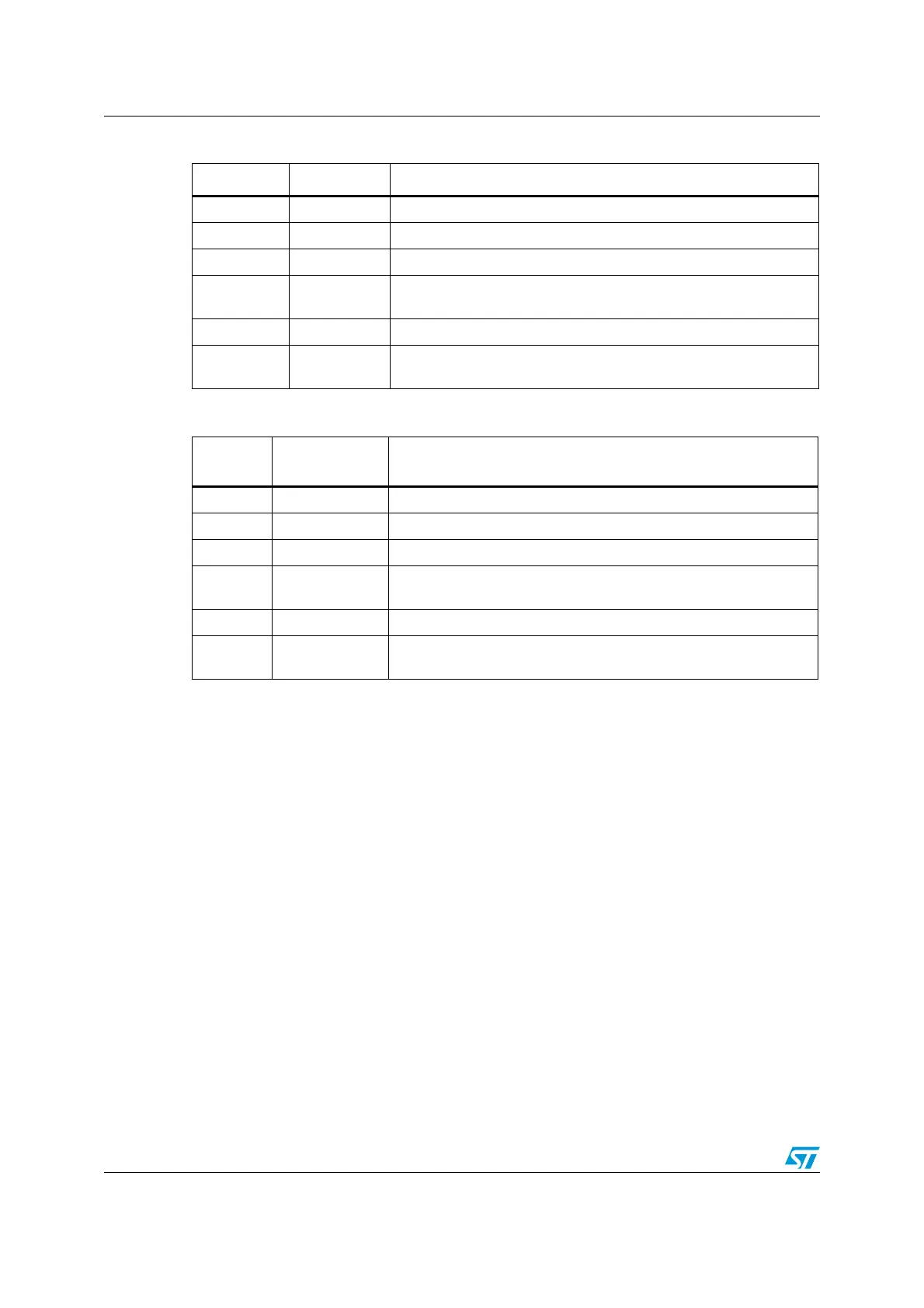

Table 114. FSMC_BTRx bit fields

Bit number Bit name Value to set

31-30 0x0

29-28 ACCMOD 0x1 if extended mode is set

27-16 0x000

15-8 DATAST

Duration of the access second phase (DATAST+3 HCLK cycles) in

read. This value can not be 0 (minimum is 1)

7-4 0x0

3-0 ADDSET

Duration of the access first phase (ADDSET+1 HCLK cycles) in

read.

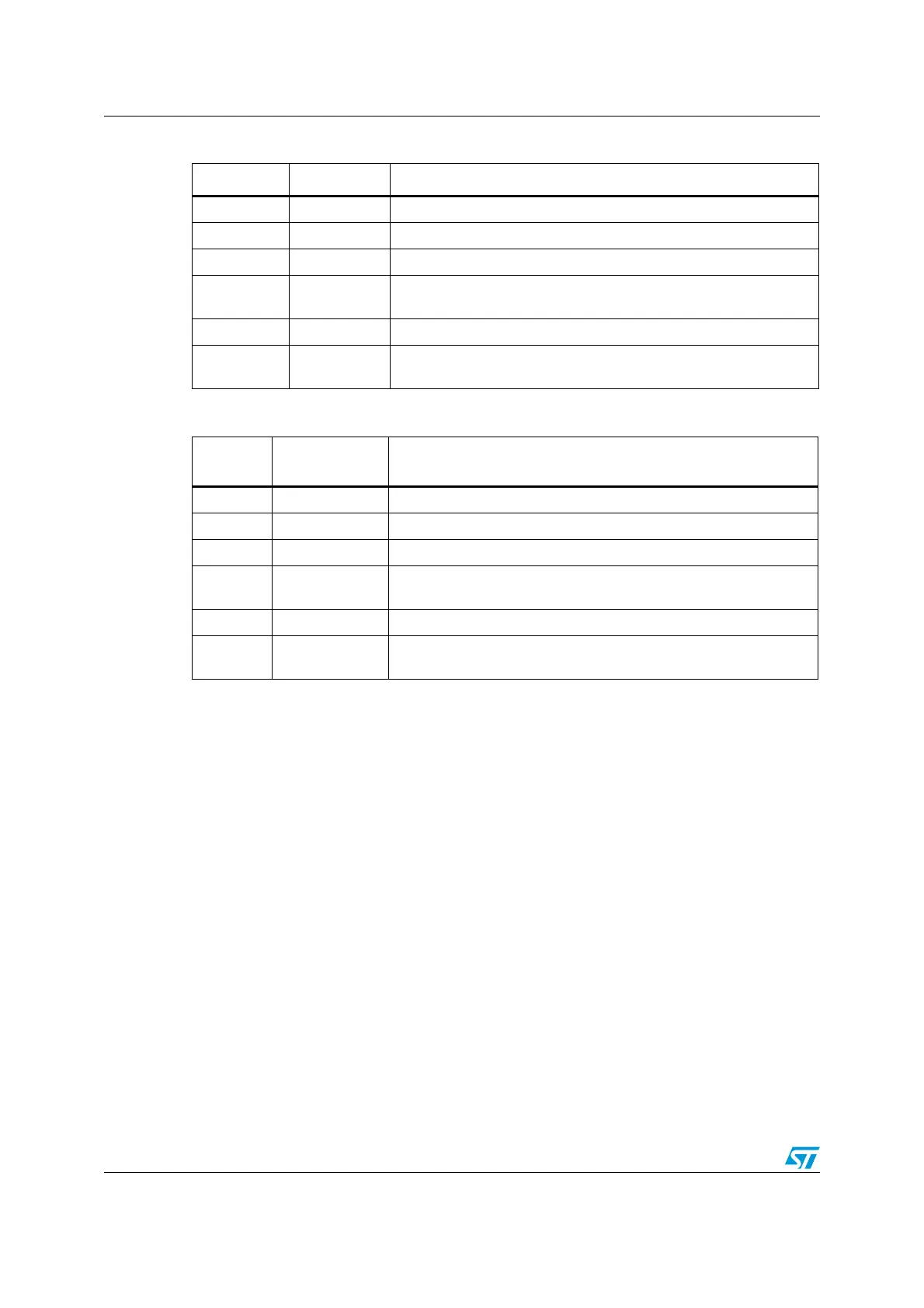

Table 115. FSMC_BWTRx bit fields

Bit

number

Bit name Value to set

31-30 0x0

29-28 ACCMOD 0x1 if extended mode is set

27-16 0x000

15-8 DATAST

Duration of the access second phase (DATAST+1 HCLK cycles) in

write. This value can not be 0 (minimum is 1).

7-4 0x0

3-0 ADDSET

Duration of the access first phase (ADDSET+1 HCLK cycles) in

write.

Loading...

Loading...