Analog-to-digital converter (ADC) RM0008

224/1096 Doc ID 13902 Rev 12

Figure 36. Alternate + Regular simultaneous

If a trigger occurs during an injected conversion that has interrupted a regular conversion, it

will be ignored. Figure 37 shows the behavior in this case (2nd trig is ignored).

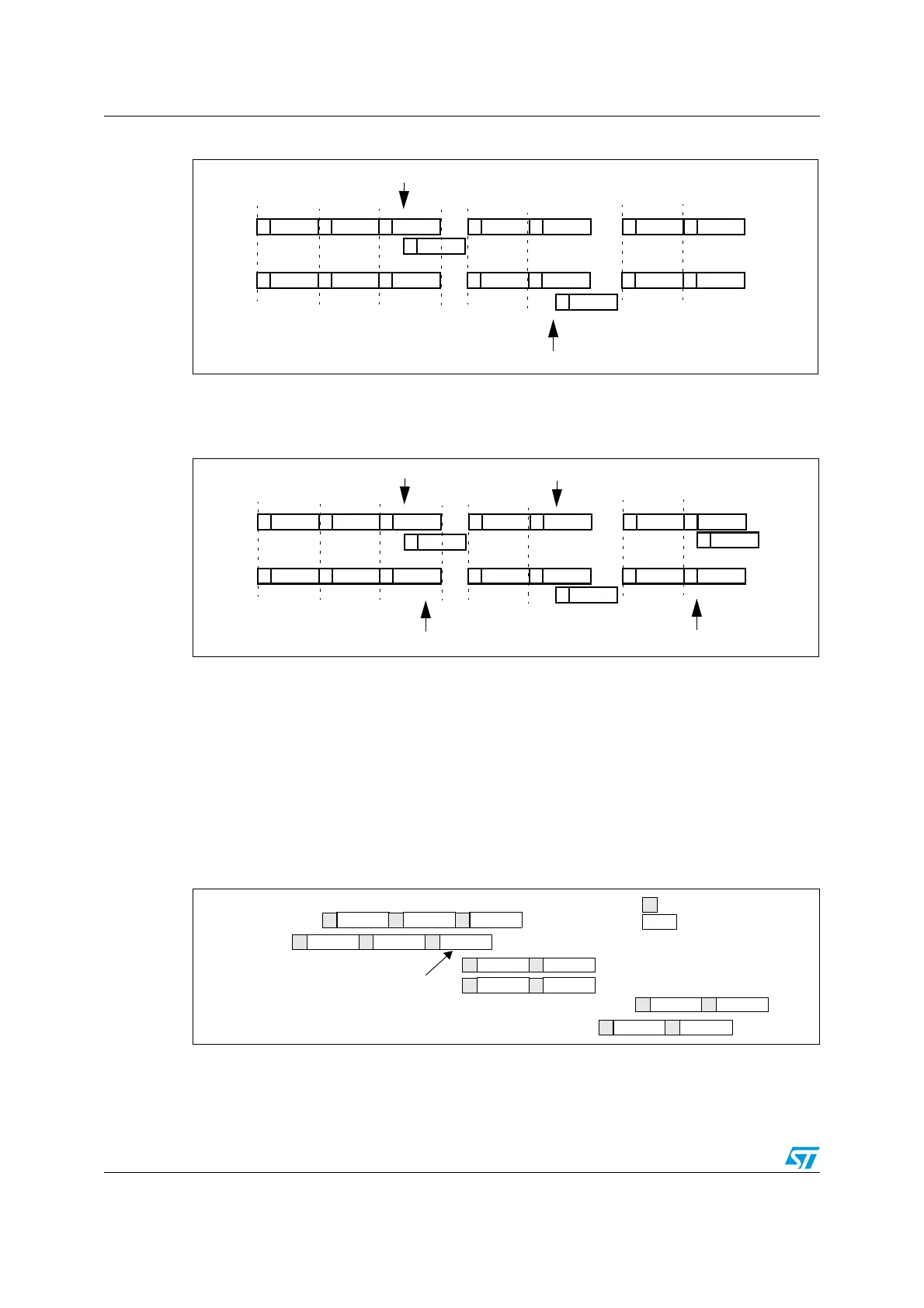

Figure 37. Case of trigger occurring during injected conversion

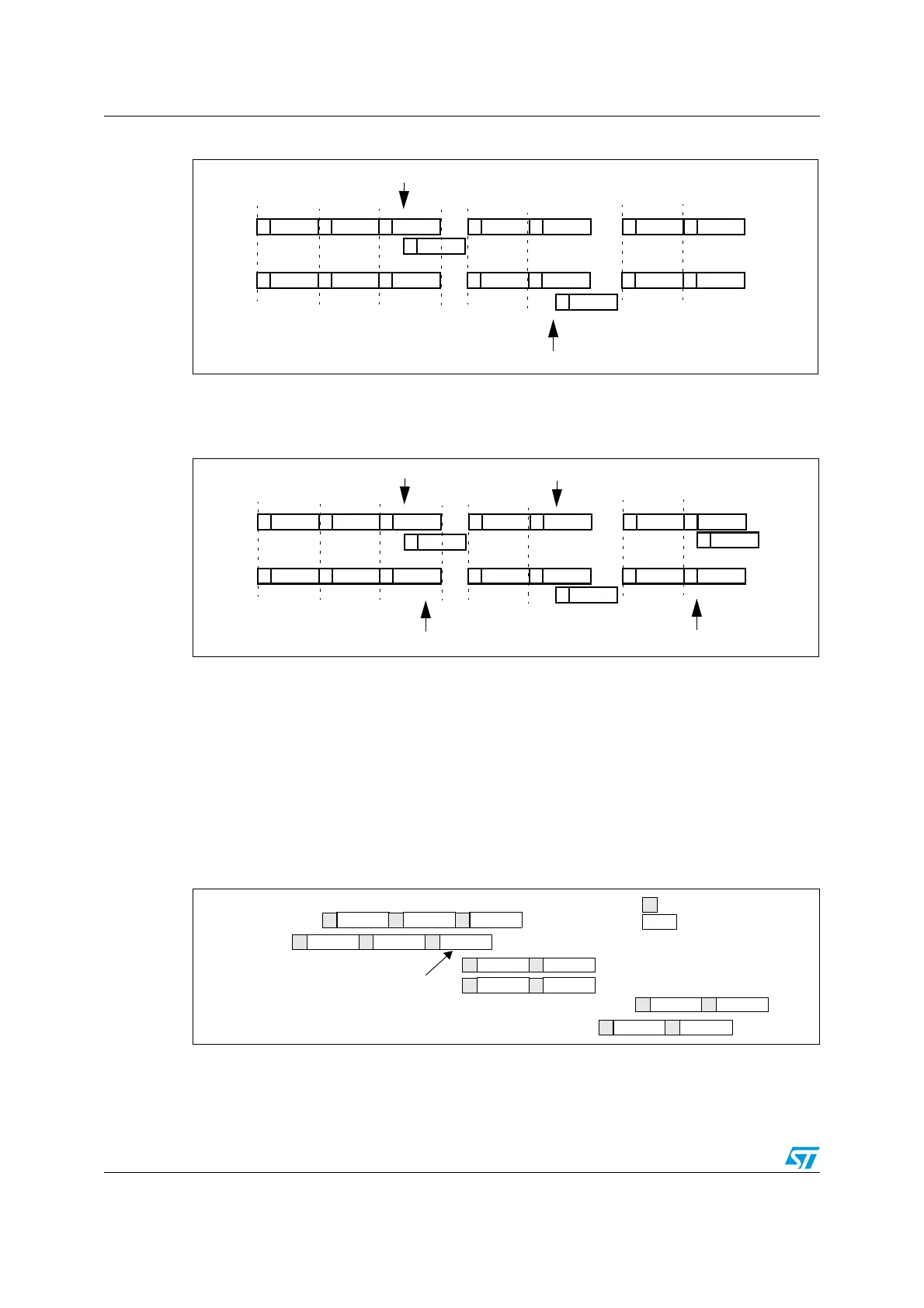

11.9.9 Combined injected simultaneous + interleaved

It is possible to interrupt an interleaved conversion with an injected event. In this case the

interleaved conversion is interrupted and the injected conversion starts, at the end of the

injected sequence the interleaved conversion is resumed. Figure 38 shows the behavior

using an example.

Note: When the ADC clock prescaler is set to 4, the interleaved mode does not recover with

evenly spaced sampling periods: the sampling interval is 8 ADC clock periods followed by 6

ADC clock periods, instead of 7 clock periods followed by 7 clock periods.

Figure 38. Interleaved single channel with injected sequence CH11, CH12

ADC1 reg

CH0 CH1 CH2

CH0

CH2 CH3

CH0

ADC1 inj

ADC2 reg

ADC2 inj

1st trig

2nd trig

synchro not lost

CH3 CH5 CH6 CH6 CH7

CH3 CH4

CH7 CH8

ADC1 reg

CH0 CH1 CH2

CH0

CH2 CH3

CH0

ADC1 inj

ADC2 reg

ADC2 inj

1st trig

4th trig

CH3 CH5 CH6 CH6 CH7

CH3 CH4

CH7 CH8

2nd trig

3rd trig

CH0

CH0

ADC2

ADC1

Trigger

Conversion

Sampling

CH0 CH0

CH0 CH0 CH0

CH11 CH12

CH12 CH11

CH0 CH0

CH0 CH0

Loading...

Loading...