Advanced-control timers (TIM1&TIM8) RM0008

284/1096 Doc ID 13902 Rev 12

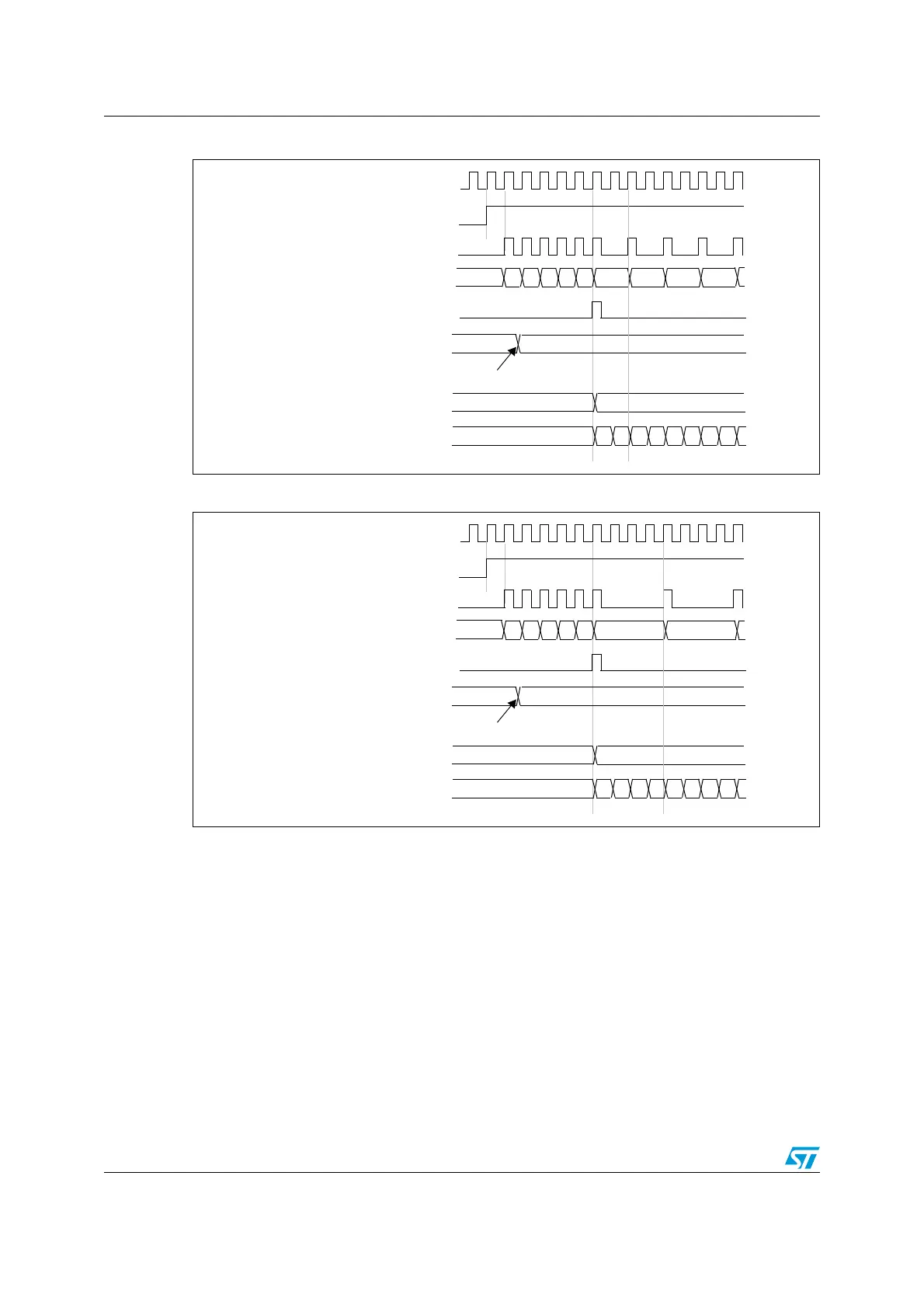

Figure 53. Counter timing diagram with prescaler division change from 1 to 2

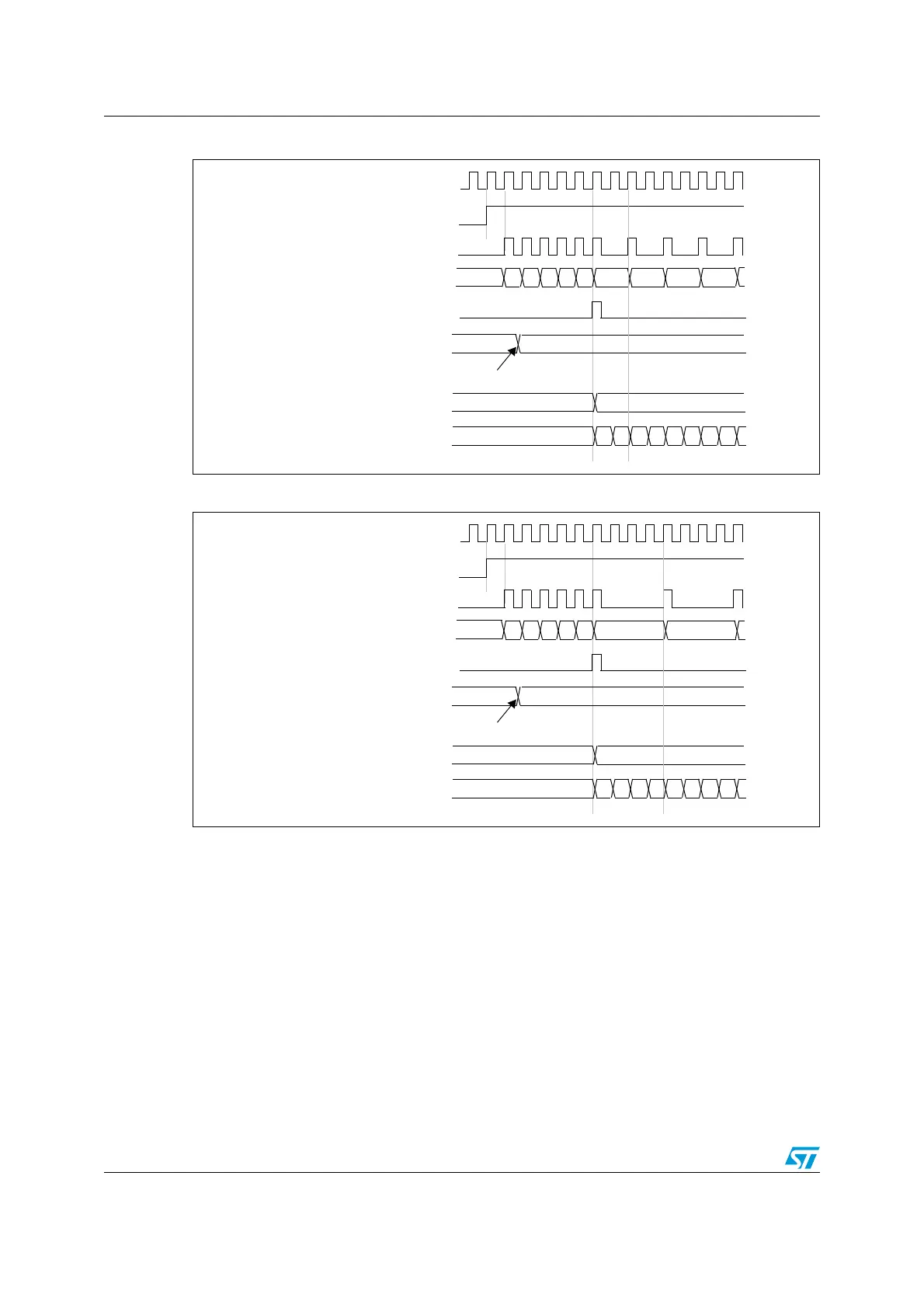

Figure 54. Counter timing diagram with prescaler division change from 1 to 4

14.3.2 Counter modes

Upcounting mode

In upcounting mode, the counter counts from 0 to the auto-reload value (content of the

TIMx_ARR register), then restarts from 0 and generates a counter overflow event.

If the repetition counter is used, the update event (UEV) is generated after upcounting is

repeated for the number of times programmed in the repetition counter register

(TIMx_RCR). Else the update event is generated at each counter overflow.

Setting the UG bit in the TIMx_EGR register (by software or by using the slave mode

controller) also generates an update event.

The UEV event can be disabled by software by setting the UDIS bit in the TIMx_CR1

register. This is to avoid updating the shadow registers while writing new values in the

CK_PSC

00

CEN

Timer clock = CK_CNT

Counter register

Update event (UEV)

0

F9 FA FB FCF7

Prescaler control register

01

Write a new value in TIMx_PSC

01 02 03

Prescaler buffer

01

Prescaler counter

0

1 0 1 0 1 0 1

F8

CK_PSC

00

CEN

Timer clock = CK_CNT

Counter register

Update event (UEV)

0

F9 FA FB FCF7

Prescaler control register

03

Write a new value in TIMx_PSC

Prescaler buffer

03

Prescaler counter

0

1 2 3 0 1 2 3

F8 01

Loading...

Loading...