Basic timers (TIM6&TIM7) RM0008

454/1096 Doc ID 13902 Rev 12

Prescaler description

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It

is based on a 16-bit counter controlled through a 16-bit register (in the TIMx_PSC register).

It can be changed on the fly as the TIMx_PSC control register is buffered. The new

prescaler ratio is taken into account at the next update event.

Figure 170 and Figure 171 give some examples of the counter behavior when the prescaler

ratio is changed on the fly.

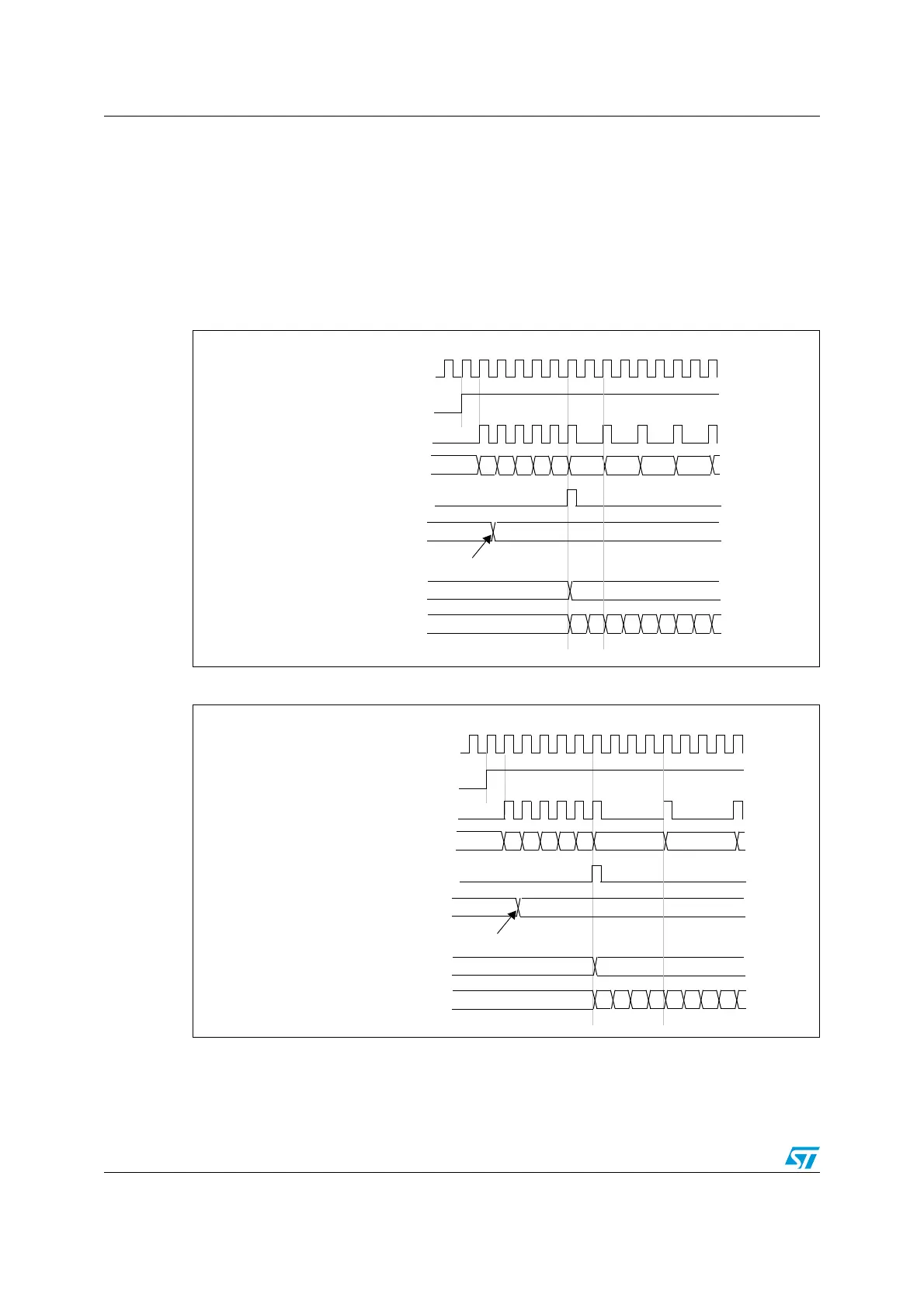

Figure 170. Counter timing diagram with prescaler division change from 1 to 2

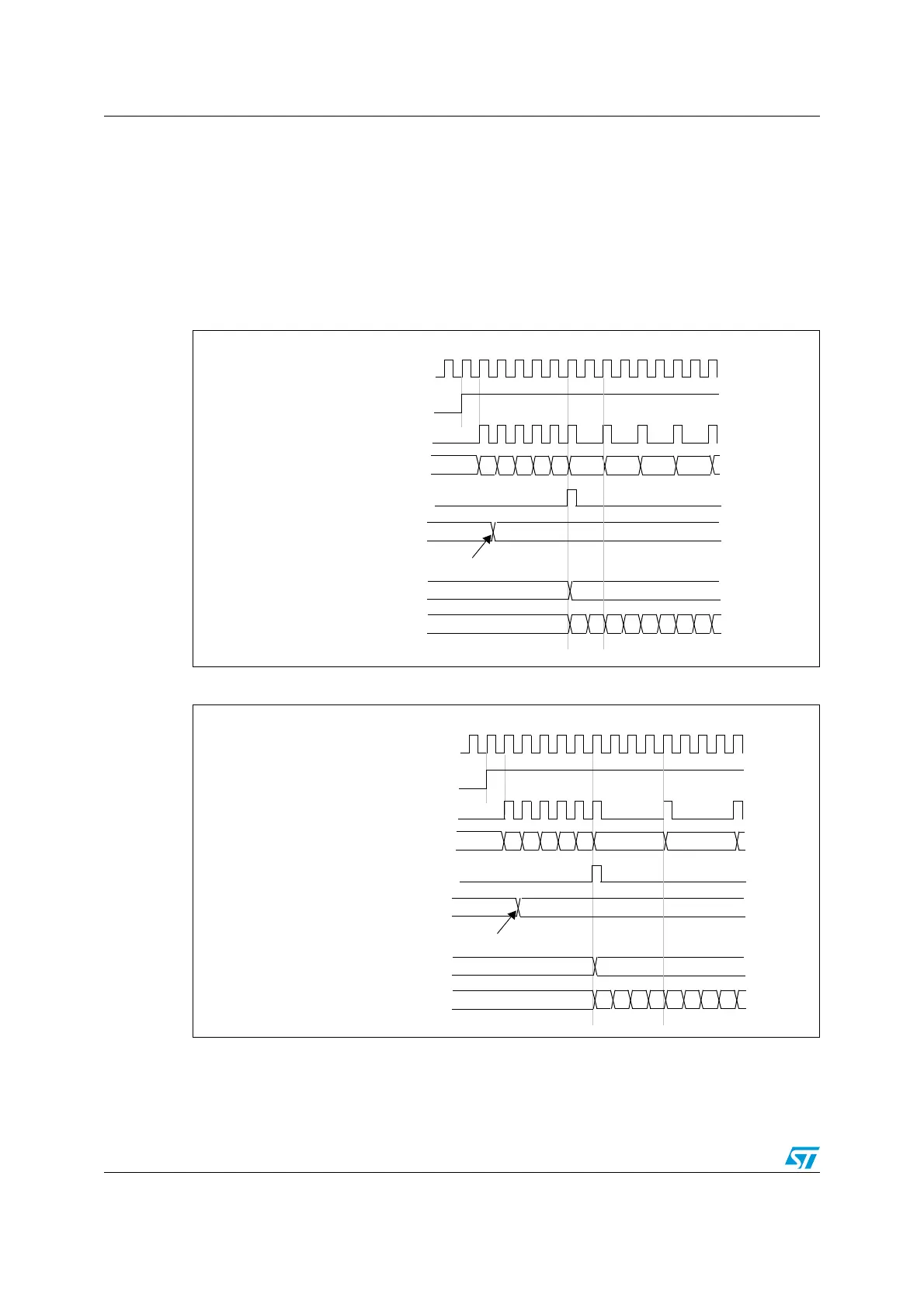

Figure 171. Counter timing diagram with prescaler division change from 1 to 4

CK_PSC

00

CNT_EN

Timer clock = CK_CNT

Counter register

Update event (UEV)

0

F9 FA FB FCF7

Prescaler control register

01

Write a new value in TIMx_PSC

01 02 03

Prescaler buffer

01

Prescaler counter

0

1 0 1 0 1 0 1

F8

CK_PSC

00

CNT_EN

Timer clock = CK_CNT

Counter register

Update event (UEV)

0

F9 FA FB FCF7

Prescaler control register

03

Write a new value in TIMx_PSC

Prescaler buffer

03

Prescaler counter

0

1 2 3 0 1 2 3

F8 01

Loading...

Loading...