Connectivity line devices: reset and clock control (RCC) RM0008

148/1096 Doc ID 13902 Rev 12

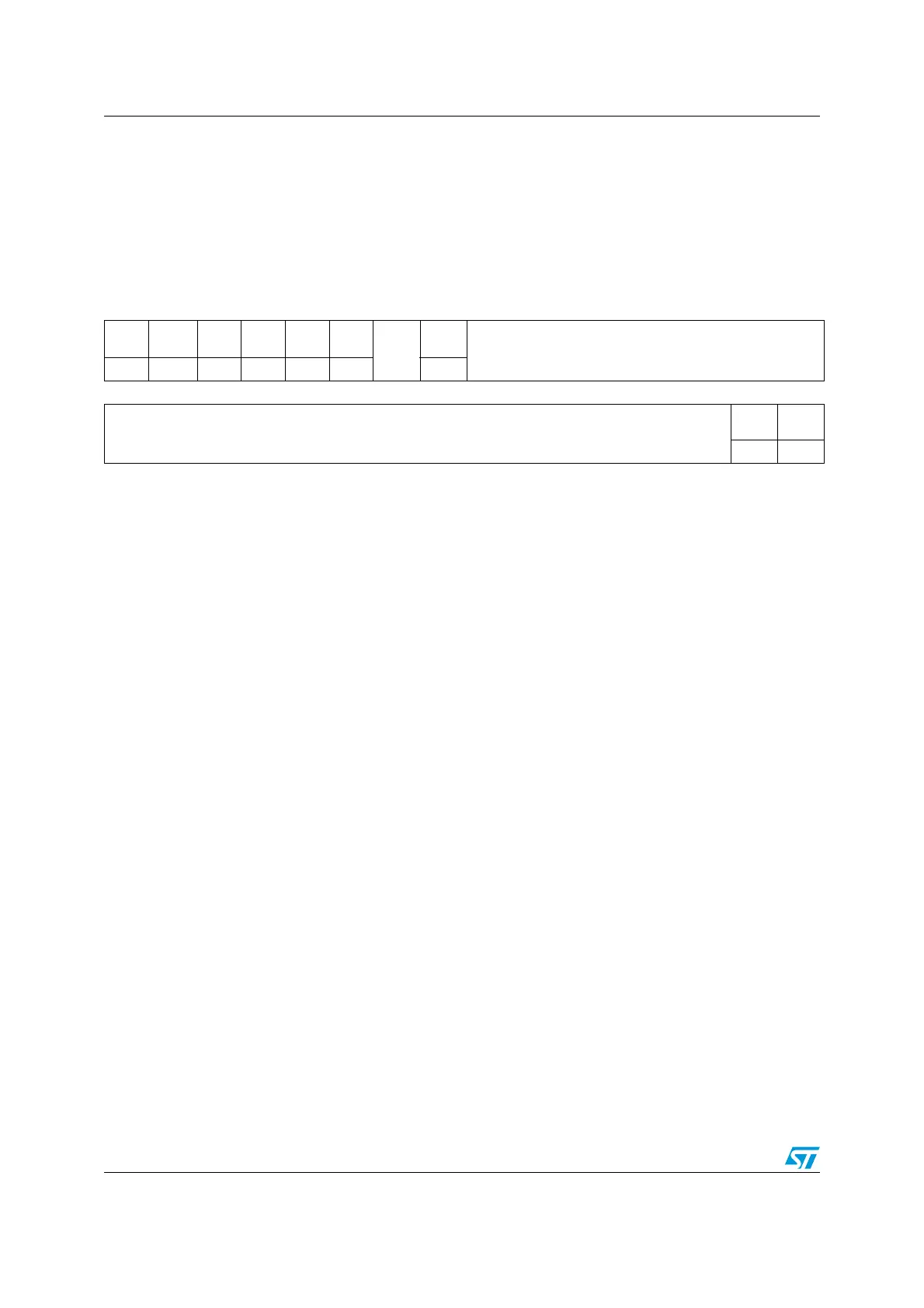

8.3.10 Control/status register (RCC_CSR)

Address: 0x24

Reset value: 0x0C00 0000, reset by system Reset, except reset flags by power Reset only.

Access: 0 ≤ wait state ≤ 3, word, half-word and byte access

Wait states are inserted in the case of successive accesses to this register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LPWR

RSTF

WWDG

RSTF

IWDG

RSTF

SFT

RSTF

POR

RSTF

PIN

RSTF

Res.

RMVF

Reserved

rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

LSI

RDY

LSION

rrw

Bit 31 LPWRRSTF: Low-power reset flag

Set by hardware when a Low-power management reset occurs. It is cleared by writing to the

RMVF bit.

0: No Low-power management reset occurred

1: Low-power management reset occurred

For further information on Low-power management reset, refer to Section : Low-power

management reset.

Bit 30 WWDGRSTF: Window watchdog reset flag

Set by hardware when a window watchdog reset occurs. It is cleared by writing to the RMVF

bit.

0: No window watchdog reset occurred

1: Window watchdog reset occurred

Bit 29 IWDGRSTF: Independent watchdog reset flag

Set by hardware when an independent watchdog reset from V

DD

domain occurs. It is cleared

by writing to the RMVF bit.

0: No watchdog reset occurred

1: Watchdog reset occurred

Bit 28 SFTRSTF: Software reset flag

Set by hardware when a software reset occurs. It is cleared by writing to the RMVF bit.

0: No software reset occurred

1: Software reset occurred

Bit 27 PORRSTF: POR/PDR reset flag

Set by hardware when a POR/PDR reset occurs. It is cleared by writing to the RMVF bit.

0: No POR/PDR reset occurred

1: POR/PDR reset occurred

Bit 26 PINRSTF: PIN reset flag

Set by hardware when a reset from the NRST pin occurs. It is cleared by writing to the

RMVF bit.

0: No reset from NRST pin occurred

1: Reset from NRST pin occurred

Bit 25 Reserved, always read as 0.

Loading...

Loading...