RM0008 Analog-to-digital converter (ADC)

Doc ID 13902 Rev 12 207/1096

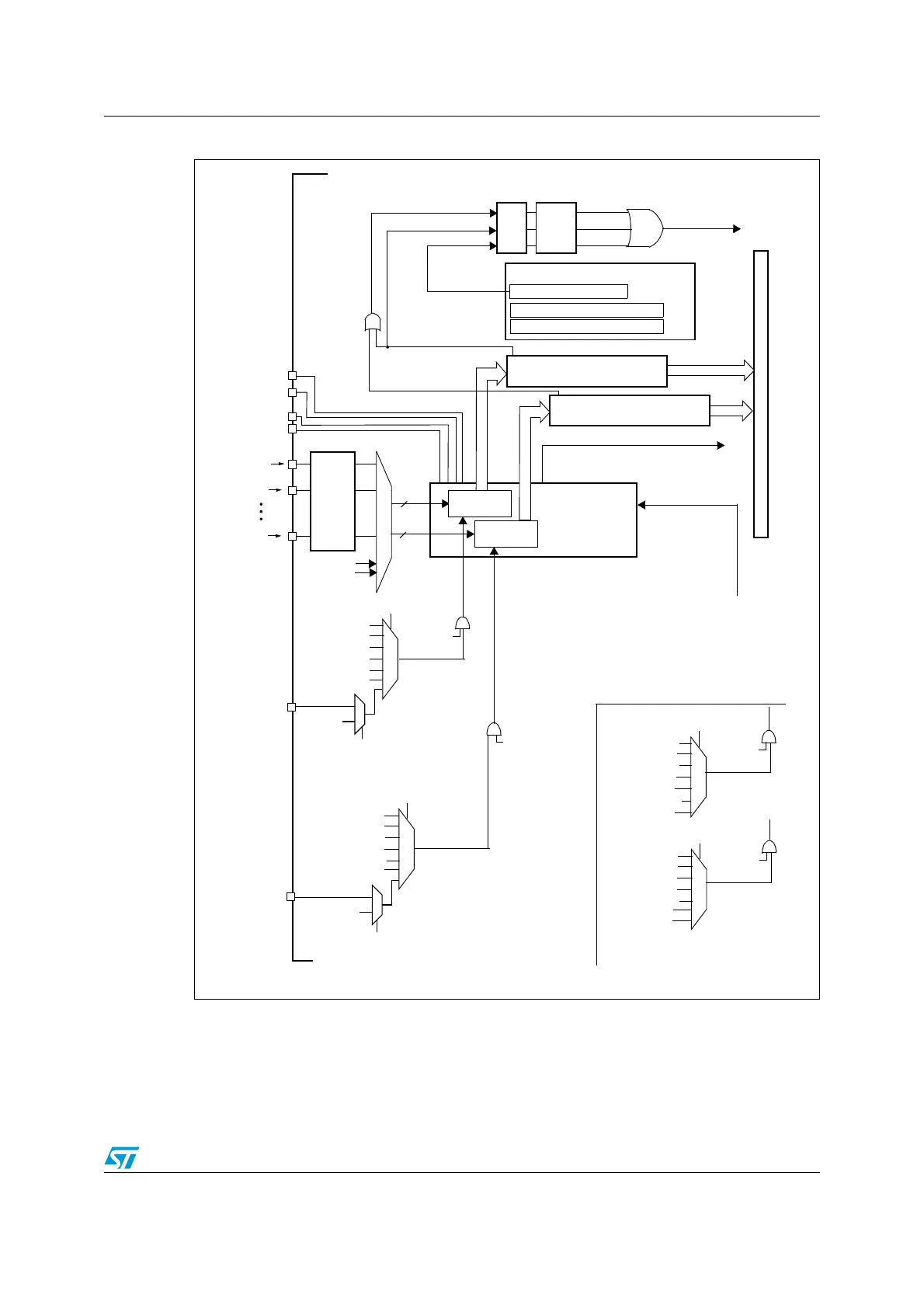

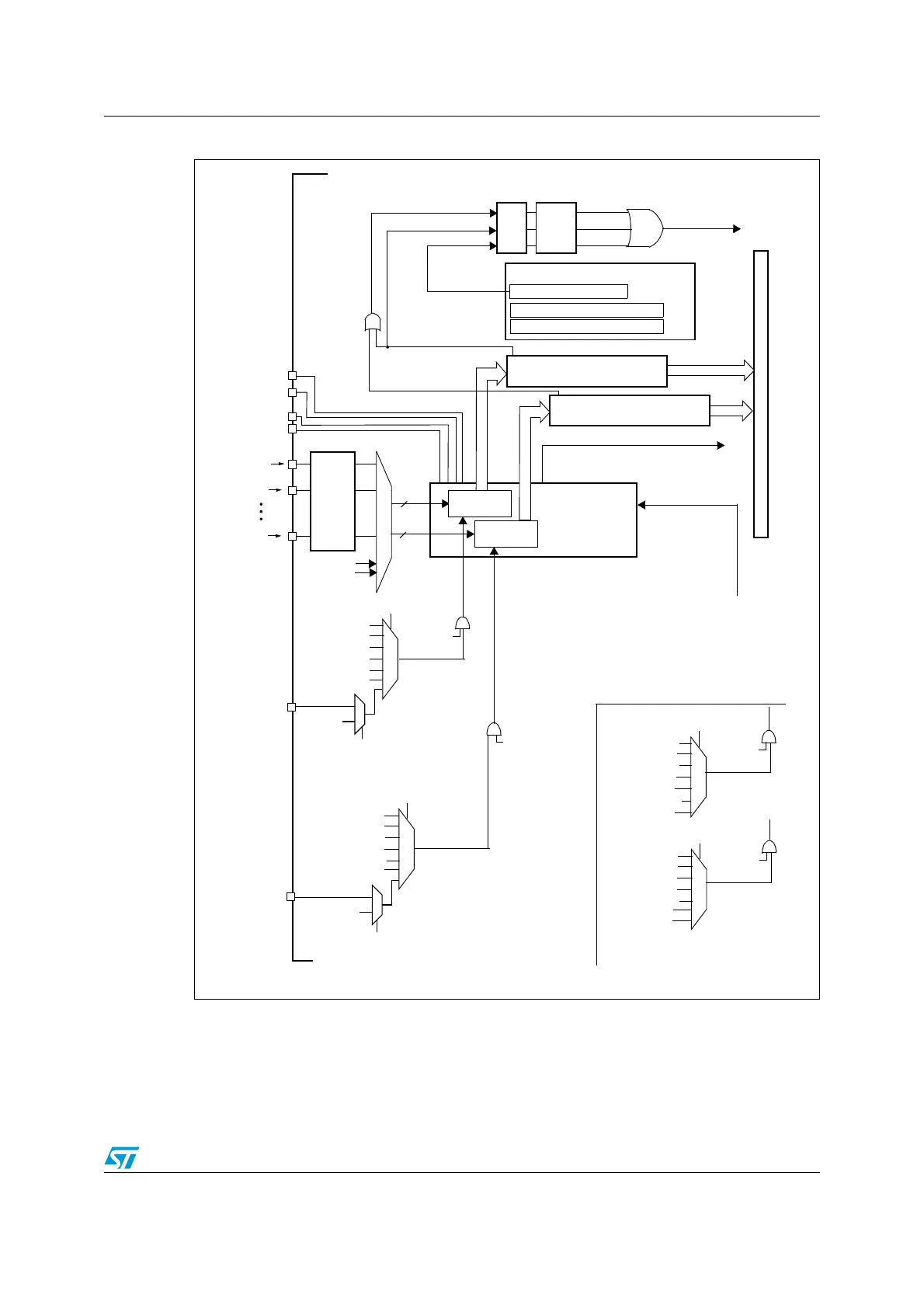

Figure 22. Single ADC block diagram

1. ADC3 has regular and injected conversion triggers different from those of ADC1 and ADC2.

2. TIM8_CH4 and TIM8_TRGO with their corresponding remap bits exist only in High-density and XL-density

products.

ADCx_IN0

ADCx_IN1

Analog to digital

converter

ADCx_IN15

Analog

MUX

ADCCLK

ADC Interrupt to NVIC

GPIO

Ports

Analog watchdog

Address/data bus

Low Threshold (12 bits)

Compare Result

High Threshold (12 bits)

Flags

enable bits

EOC

AWD

Analog watchdog event

V

DDA

V

SSA

V

REF+

V

REF-

Interrupt

TIM1_CH2

TIM1_CH3

TIM2_CH2

TIM3_CH4

From ADC prescaler

(16 bits)

End of conversion

channels

Injected

channels

End of injected conversion

JEOC

EOCIE

AWDIE

JEOCIE

up to 4

up to 16

Regular data register

(4 x 16 bits)

Injected data registers

Regular

Start trigger

(regular group)

EXTSEL[2:0] bits

EXTRIG

TIM1_CH1

TIM4_TRGO

EXTI_15

TIM1_CH4

TIM2_TRGO

TIM2_CH1

TIM3_TRGO

Start trigger

(injected group)

JEXTSEL[2:0] bits

TIM1_TRGO

TIM4_CH4

JEXTRIG

bit

bit

DMA request

Temp. sensor

V

REFINT

TIM2_CH3

TIM1_CH3

TIM8_CH1

TIM8_CH4

TIM3_CH1

TIM5_TRGO

TIM1_CH4

TIM4_CH3

TIM8_CH2

TIM8_TRGO

JEXTSEL[2:0] bits

TIM1_TRGO

TIM5_CH1

Triggers for ADC3

(1)

Start trigger

(injected group)

JEXTRIG

bit

Start trigger

(regular group)

EXTRIG

bit

EXTSEL[2:0] bits

TIM5_CH4

TIM5_CH3

EXTI_11

TIM8_TRGO

(2)

ADCx_ETRGREG_REMAP bit

TIM8_CH4

(2)

ADCx-ETRGINJ_REMAP bit

ai14802d

Loading...

Loading...