RM0008 Ethernet (ETH): media access control (MAC) with DMA controller

Doc ID 13902 Rev 12 1019/1096

29.8.2 MMC register description

Ethernet MMC control register (ETH_MMCCR)

Address offset: 0x0100

Reset value: 0x0000 0000

The Ethernet MMC Control register establishes the operating mode of the management

counters.

Ethernet MMC receive interrupt register (ETH_MMCRIR)

Address offset: 0x0104

Reset value: 0x0000 0000

The Ethernet MMC receive interrupt register maintains the interrupts generated when

receive statistic counters reach half their maximum values. (MSB of the counter is set.) It is

a 32-bit wide register. An interrupt bit is cleared when the respective MMC counter that

caused the interrupt is read. The least significant byte lane (bits [7:0]) of the respective

counter must be read in order to clear the interrupt bit.

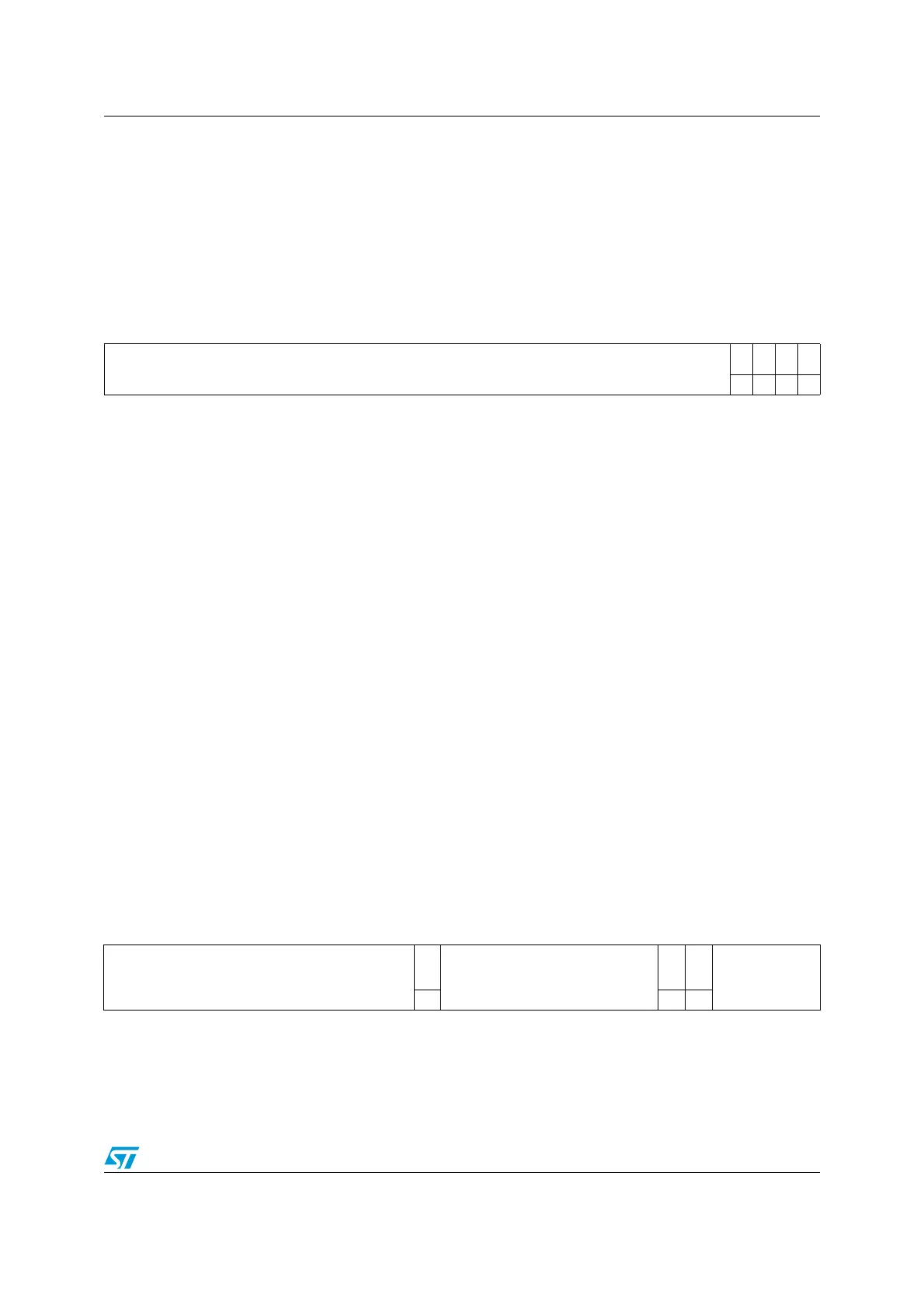

313029282726252423222120191817161514131211109876543210

Reserved

MCF

ROR

CSR

CR

rw rw rw rw

Bits 31:4 Reserved

Bit 3 MCF: MMC counter freeze

When set, this bit freezes all the MMC counters to their current value. (None of the MMC

counters are updated due to any transmitted or received frame until this bit is cleared to 0. If

any MMC counter is read with the Reset on Read bit set, then that counter is also cleared in

this mode.)

Bit 2 ROR: Reset on read

When this bit is set, the MMC counters is reset to zero after read (self-clearing after reset). The

counters are cleared when the least significant byte lane (bits [7:0]) is read.

Bit 1 CSR: Counter stop rollover

When this bit is set, the counter does not roll over to zero after it reaches the maximum value.

Bit 0 CR: Counter reset

When it is set, all counters are reset. This bit is cleared automatically after 1 clock cycle.

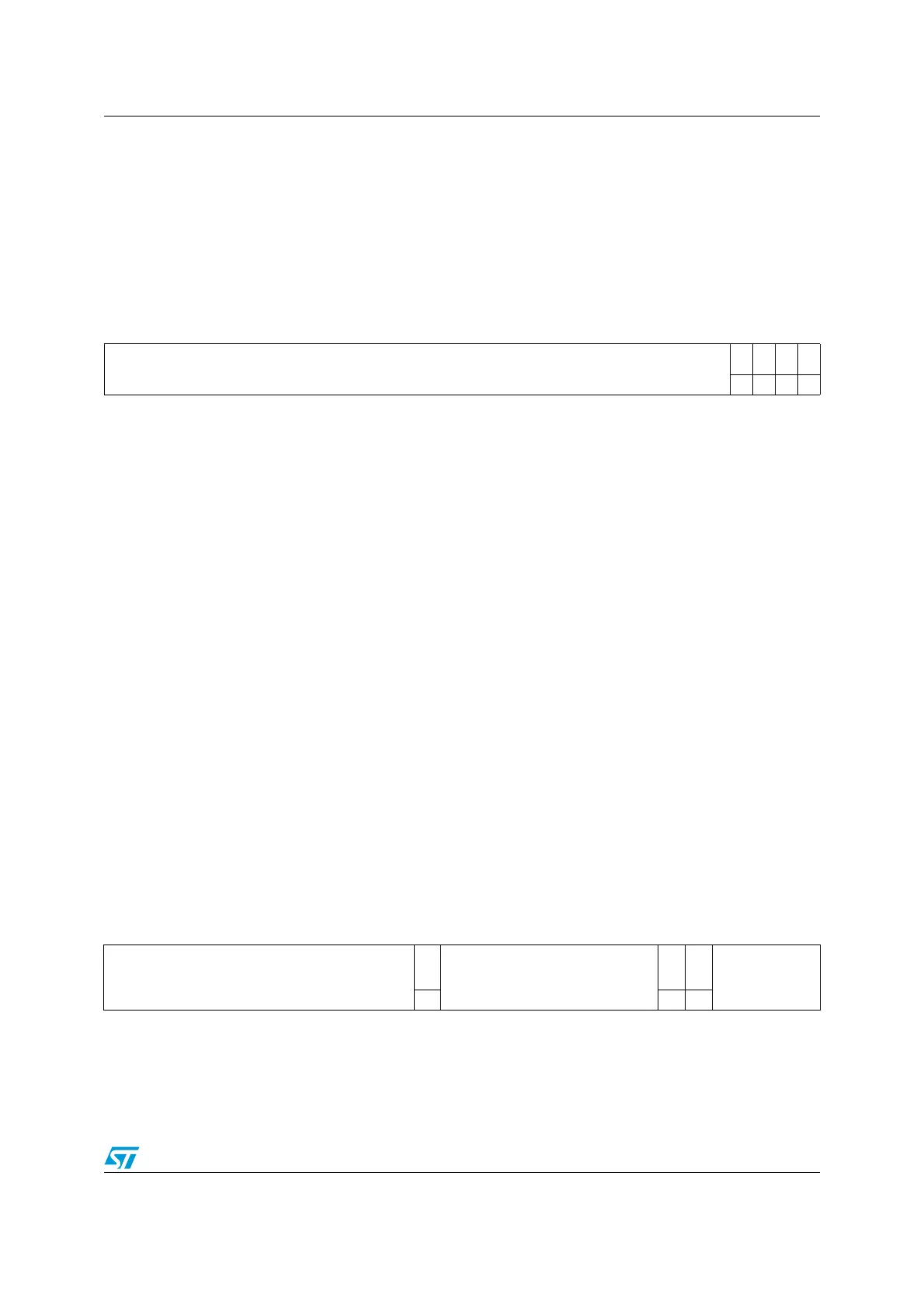

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

RGUFS

Reserved

RFAES

RFCES

Reserved

rc_r rc_r rc_r

Bits 31:18 Reserved

Bit 17 RGUFS: Received Good Unicast Frames Status

This bit is set when the received, good unicast frames, counter reaches half the maximum

value.

Loading...

Loading...