RM0008 Universal synchronous asynchronous receiver transmitter (USART)

Doc ID 13902 Rev 12 791/1096

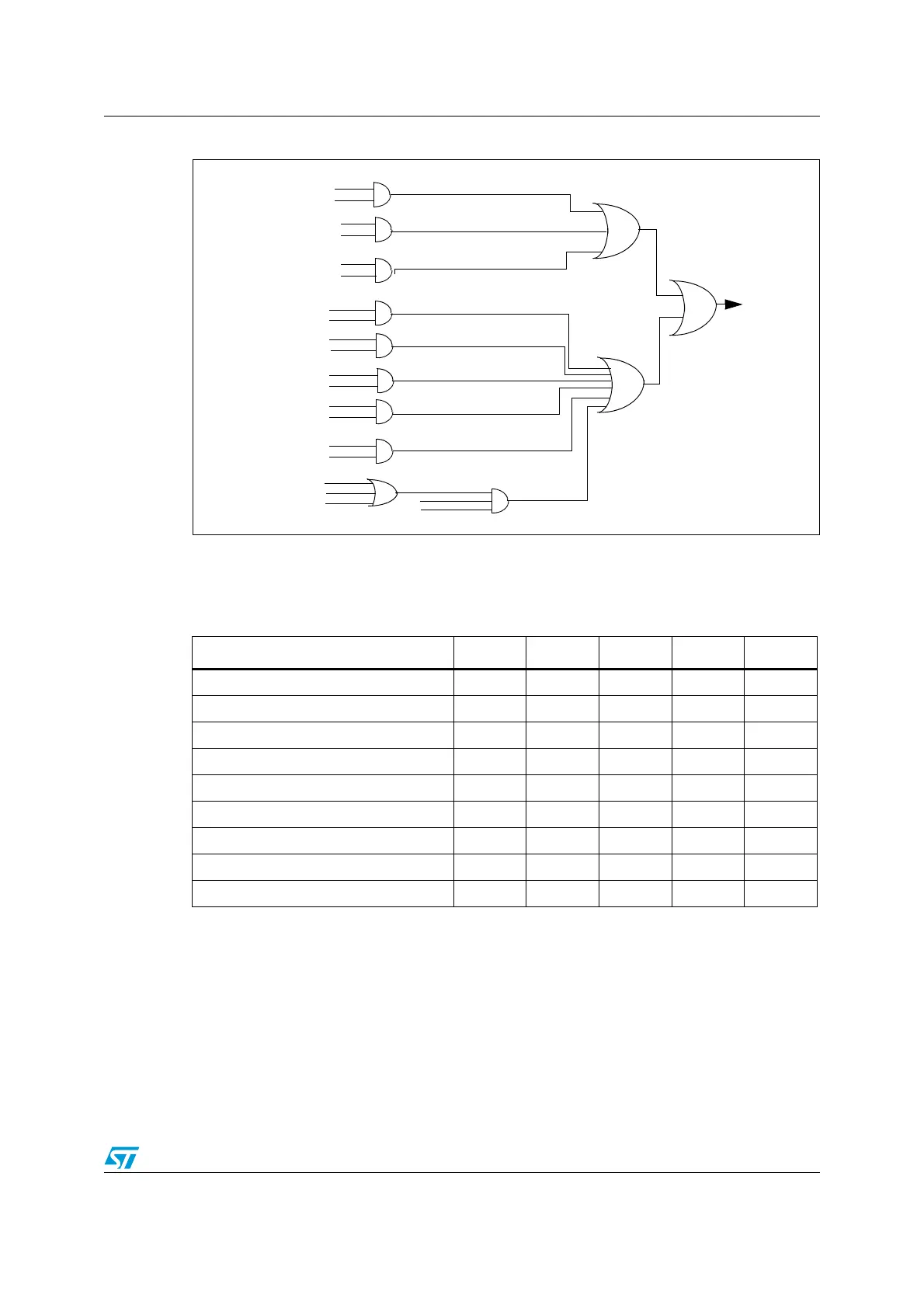

Figure 300. USART interrupt mapping diagram

27.5 USART mode configuration

27.6 USART registers

Refer to Section 2.1 on page 46 for a list of abbreviations used in register descriptions.

The peripheral registers can be accessed by half-words (16-bit) or words (32-bit).

TC

TCIE

TXE

TXEIE

IDLE

IDLEIE

RXNEIE

ORE

RXNEIE

RXNE

PE

PEIE

FE

NE

ORE

EIE

DMAR

USART

LBD

LBDIE

CTS

CTSIE

interrupt

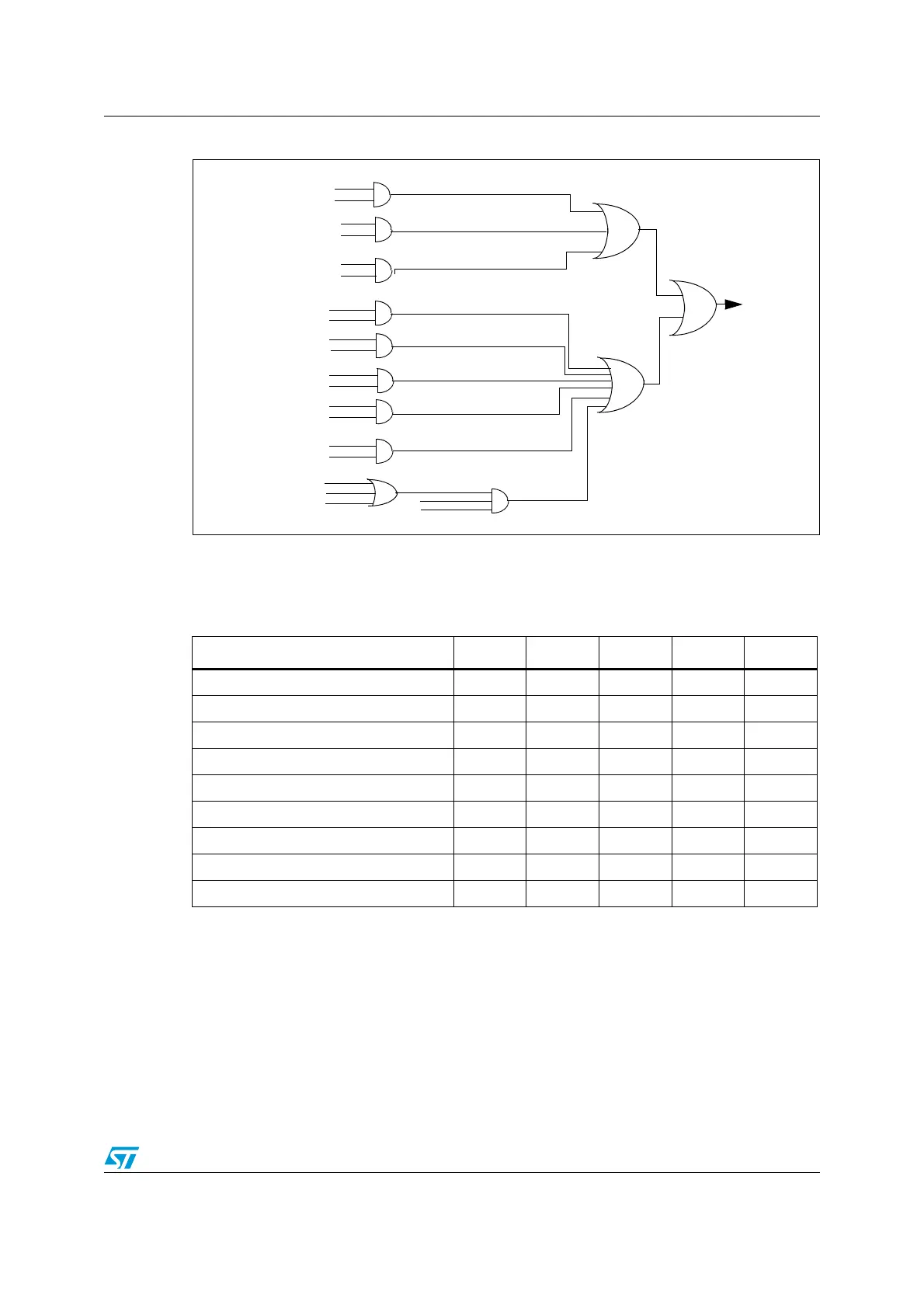

Table 196. USART mode configuration

(1)

1. X = supported; NA = not applicable.

USART modes USART1 USART2 USART3 UART4 UART5

Asynchronous mode X X X X X

Hardware Flow Control X X X NA NA

Multibuffer Communication (DMA) X X X X NA

Multiprocessor Communication X X X X X

Synchronous X X X NA NA

Smartcard XXXNANA

Half-Duplex (Single-Wire mode) X X X X X

IrDA XXXXX

LIN XXXXX

Loading...

Loading...