RM0008 Controller area network (bxCAN)

Doc ID 13902 Rev 12 649/1096

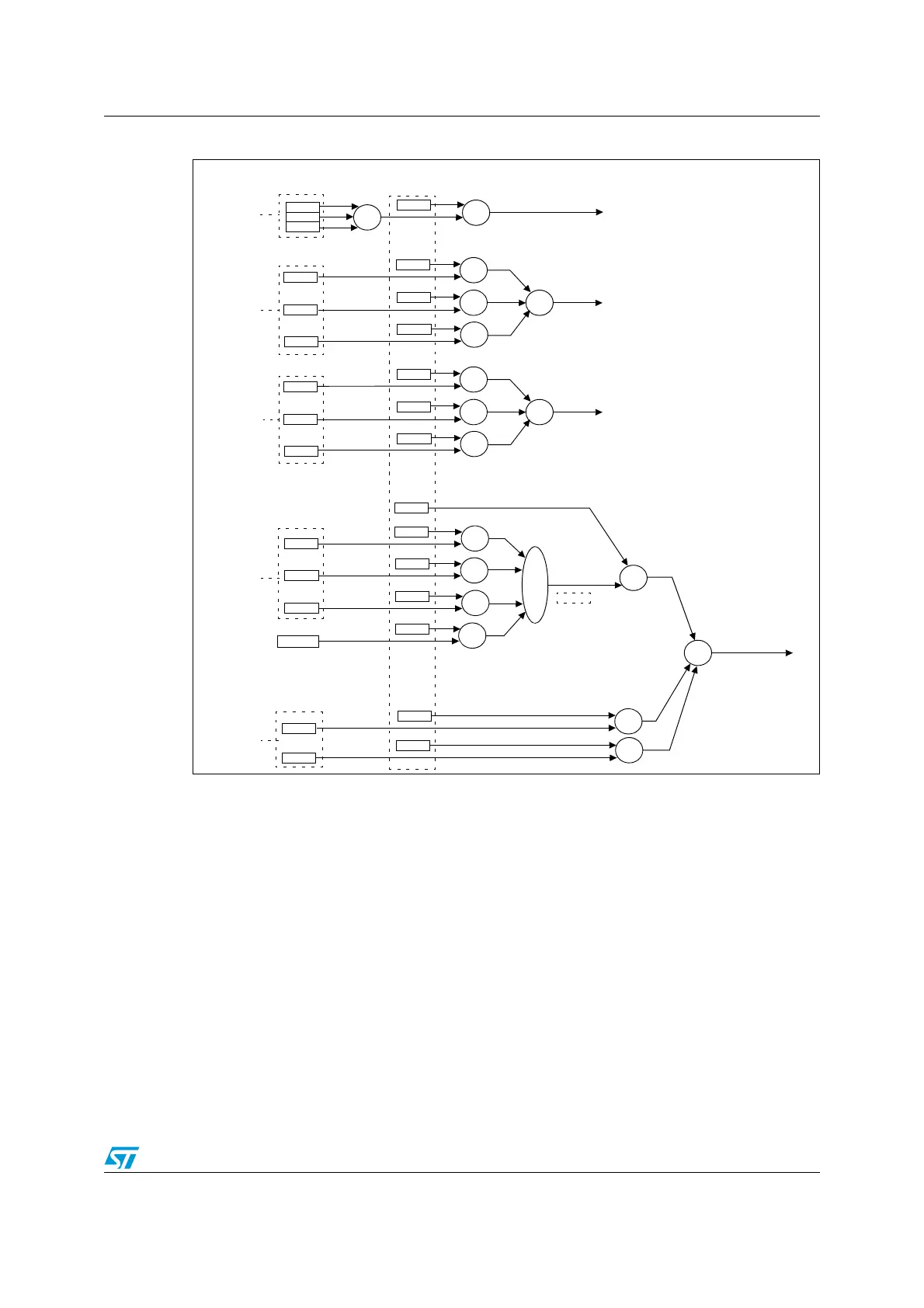

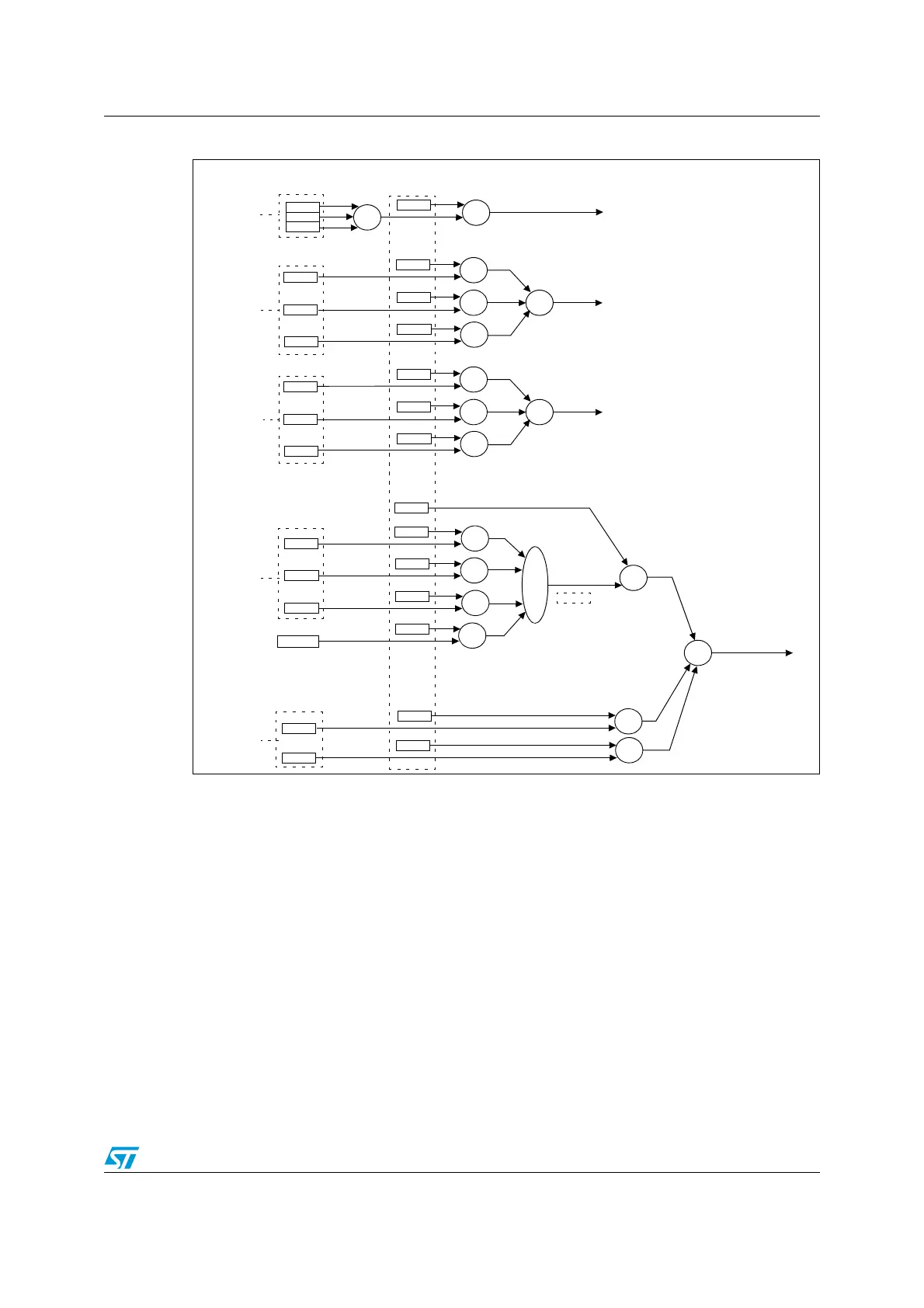

Figure 235. Event flags and interrupt generation

● The transmit interrupt can be generated by the following events:

– Transmit mailbox 0 becomes empty, RQCP0 bit in the CAN_TSR register set.

– Transmit mailbox 1 becomes empty, RQCP1 bit in the CAN_TSR register set.

– Transmit mailbox 2 becomes empty, RQCP2 bit in the CAN_TSR register set.

● The FIFO 0 interrupt can be generated by the following events:

– Reception of a new message, FMP0 bits in the CAN_RF0R register are not ‘00’.

– FIFO0 full condition, FULL0 bit in the CAN_RF0R register set.

– FIFO0 overrun condition, FOVR0 bit in the CAN_RF0R register set.

● The FIFO 1 interrupt can be generated by the following events:

– Reception of a new message, FMP1 bits in the CAN_RF1R register are not ‘00’.

– FIFO1 full condition, FULL1 bit in the CAN_RF1R register set.

– FIFO1 overrun condition, FOVR1 bit in the CAN_RF1R register set.

RQCP0

RQCP1

FMP1

CAN_TSR

+

TMEIE

CAN_IER

TRANSMIT

&

FMPIE1

FULL1

&

FFIE1

FOVR1

&

FOVIE1

&

+

CAN_RF1R

FIFO 1

EWGF

EWGIE

EPVF

EPVIE

BOFF

BOFIE

1≤LEC≤6

LECIE

&

&

&

&

CAN_ESR

+

&

ERRIE

INTERRUPT

INTERRUPT

FMP0

&

FMPIE0

FULL0

&

FFIE0

FOVR0

&

FOVIE0

+

CAN_RF0R

FIFO 0

INTERRUPT

RQCP2

WKUI

&

WKUIE

CAN_MSR

+

INTERRUPT

ERROR

STATUS CHANGE

ERRI

SLAKI

SLKIE

&

CAN_MSR

Loading...

Loading...