Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1024/1096 Doc ID 13902 Rev 12

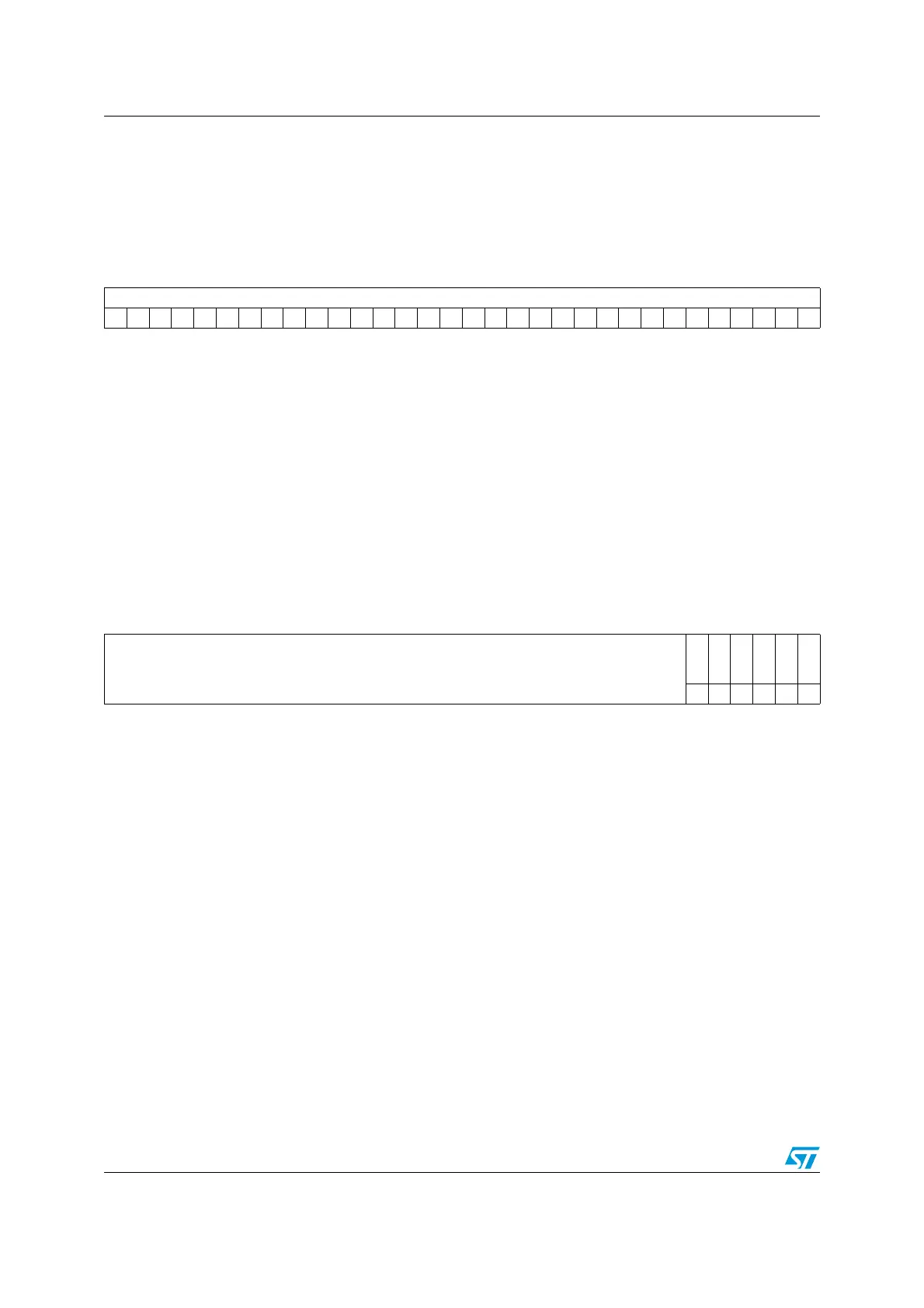

MMC received good unicast frames counter register (ETH_MMCRGUFCR)

Address offset: 0x01C4

Reset value: 0x0000 0000

This register contains the number of good unicast frames received.

29.8.3 IEEE 1588 time stamp registers

This section describes the registers required to support precision network clock

synchronization functions under the IEEE 1588 standard.

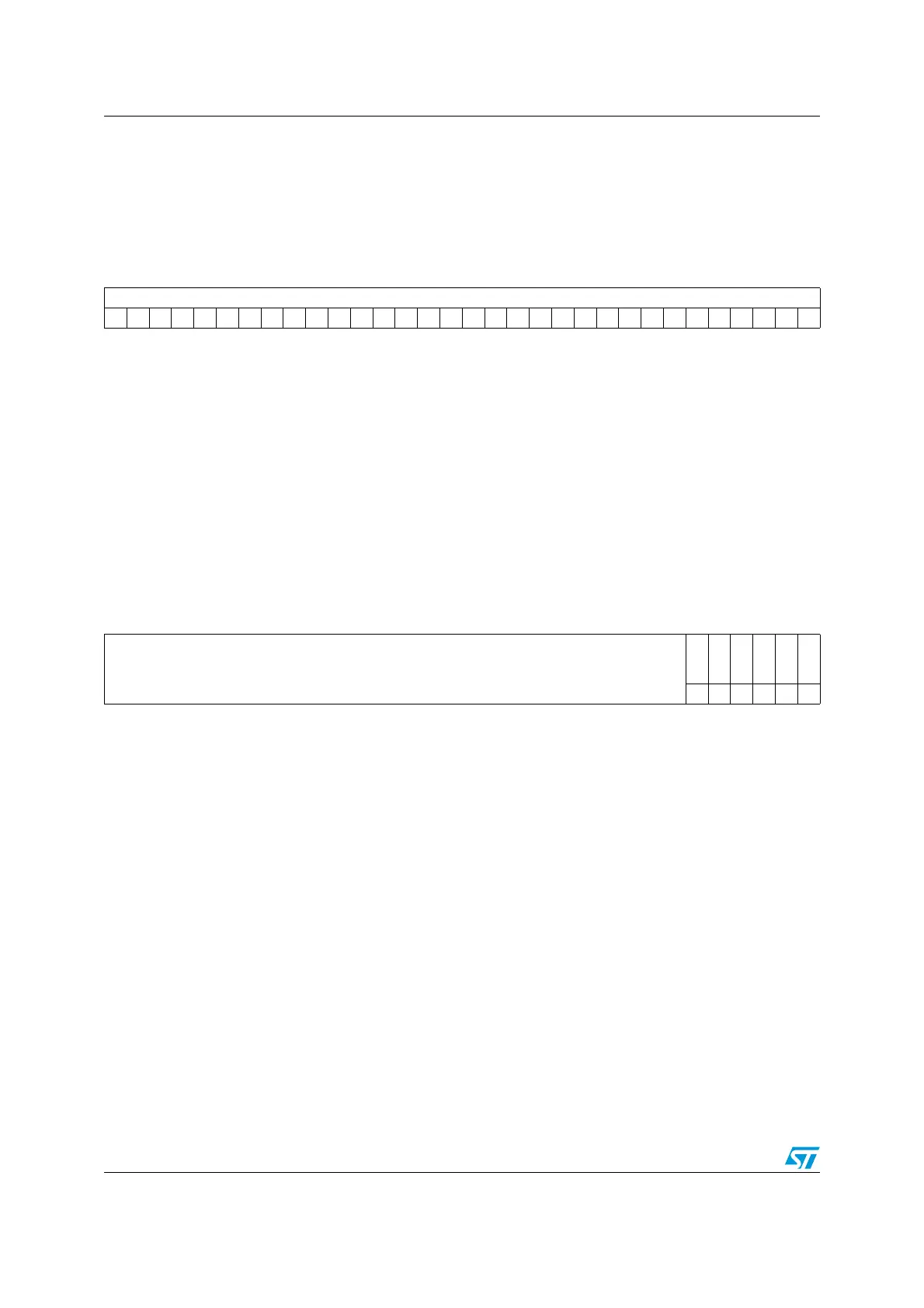

Ethernet PTP time stamp control register (ETH_PTPTSCR)

Address offset: 0x0700

Reset value: 0x0000 0000

This register controls the time stamp generation and update logic.

Ethernet PTP subsecond increment register (ETH_PTPSSIR)

313029282726252423222120191817161514131211109876543210

RGUFC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RGUFC: Received good unicast frames counter

313029282726252423222120191817161514131211109876543210

Reserved

TTSARU

TSITE

TSSTU

TSSTI

TSFCU

TSE

rw rw rw rw rw rw

Bits 31:5 Reserved

Bit 5 TSARU: Time stamp addend register update

When this bit is set, the Time stamp addend register’s contents are updated to the PTP block

for fine correction. This bit is cleared when the update is completed. This register bit must be

read as zero before you can set it.

Bit 4 TSITE: Time stamp interrupt trigger enable

When this bit is set, a time stamp interrupt is generated when the system time becomes greater

than the value written in Target Time register. When the Time Stamp Trigger interrupt is

generated, this bit is cleared.

Bit 3 TSSTU: Time stamp system time update

When this bit is set, the system time is updated (added to or subtracted from) with the value

specified in the Time stamp high update and Time stamp low update registers. Both the

TSSTU and TSSTI bits must be read as zero before you can set this bit. Once the update is

completed in hardware, this bit is cleared.

Bit 2 TSSTI: Time stamp system time initialize

When this bit is set, the system time is initialized (overwritten) with the value specified in the

Time stamp high update and Time stamp low update registers. This bit must be read as zero

before you can set it. When initialization is complete, this bit is cleared.

Loading...

Loading...