RM0008 Controller area network (bxCAN)

Doc ID 13902 Rev 12 667/1096

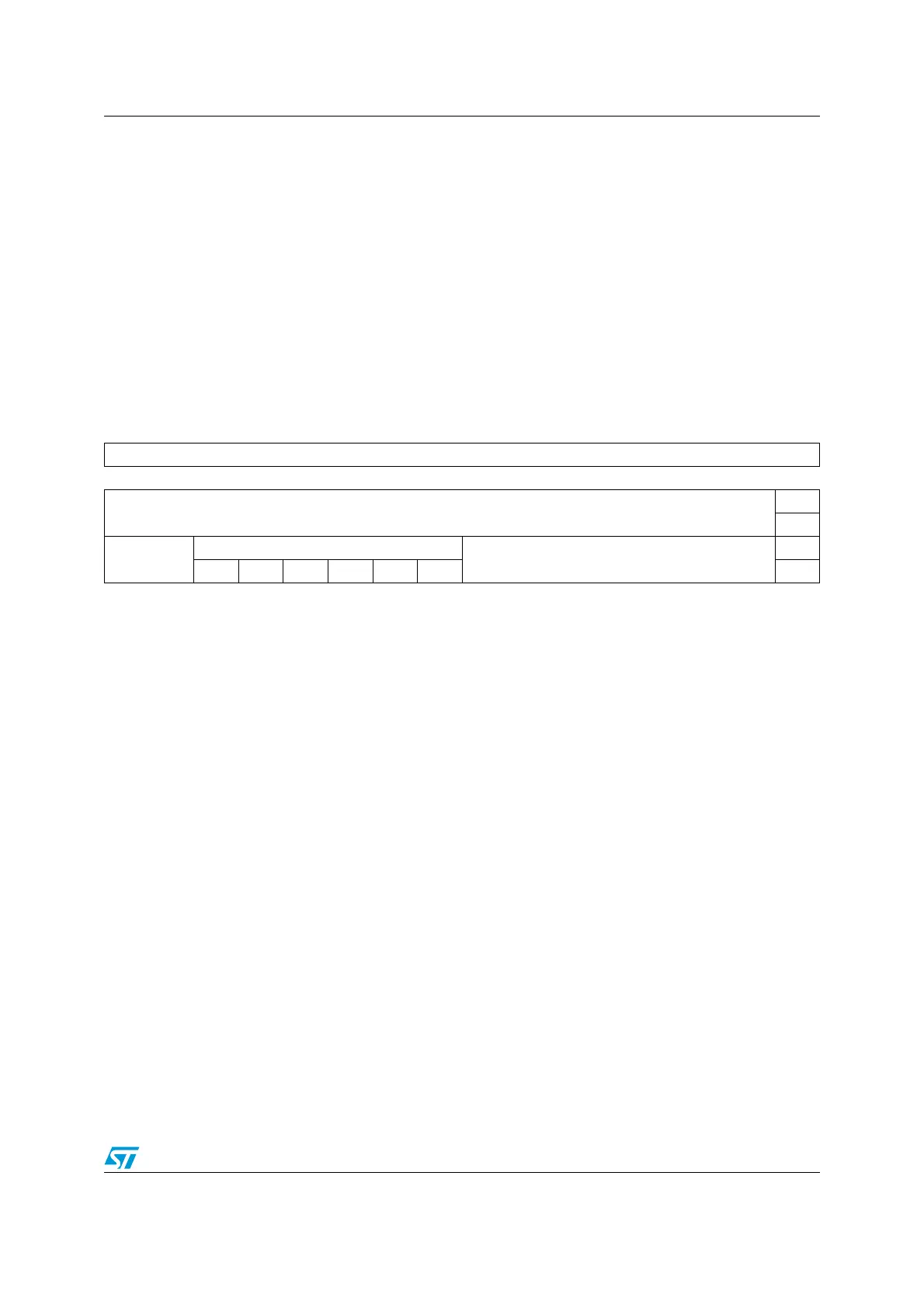

24.9.4 CAN filter registers

CAN filter master register (CAN_FMR)

Address offset: 0x200

Reset value: 0x2A1C 0E01

Note: All bits of this register are set and cleared by software.

Bits 15:8 DATA5[7:0]: Data Byte 5

Data byte 1 of the message.

Bits 7:0 DATA4[7:0]

: Data Byte 4

Data byte 0 of the message.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

FINIT

rw

Reserved

CAN2SB[5:0]

Reserved

FINIT

rw rw rw rw rw rw rw

Bits 31:14 Reserved, forced to reset value

Bits 13:8 CAN2SB[5:0]

: CAN2 start bank

These bits are set and cleared by software. They define the start bank for the CAN2

interface (Slave) in the range 1 to 27.

Note: These bits are available in connectivity line devices only and are reserved otherwise.

Bits 7:1 Reserved, forced to reset value

Bit 0 FINIT

: Filter init mode

Initialization mode for filter banks

0: Active filters mode.

1: Initialization mode for the filters.

Loading...

Loading...