Universal synchronous asynchronous receiver transmitter (USART) RM0008

790/1096 Doc ID 13902 Rev 12

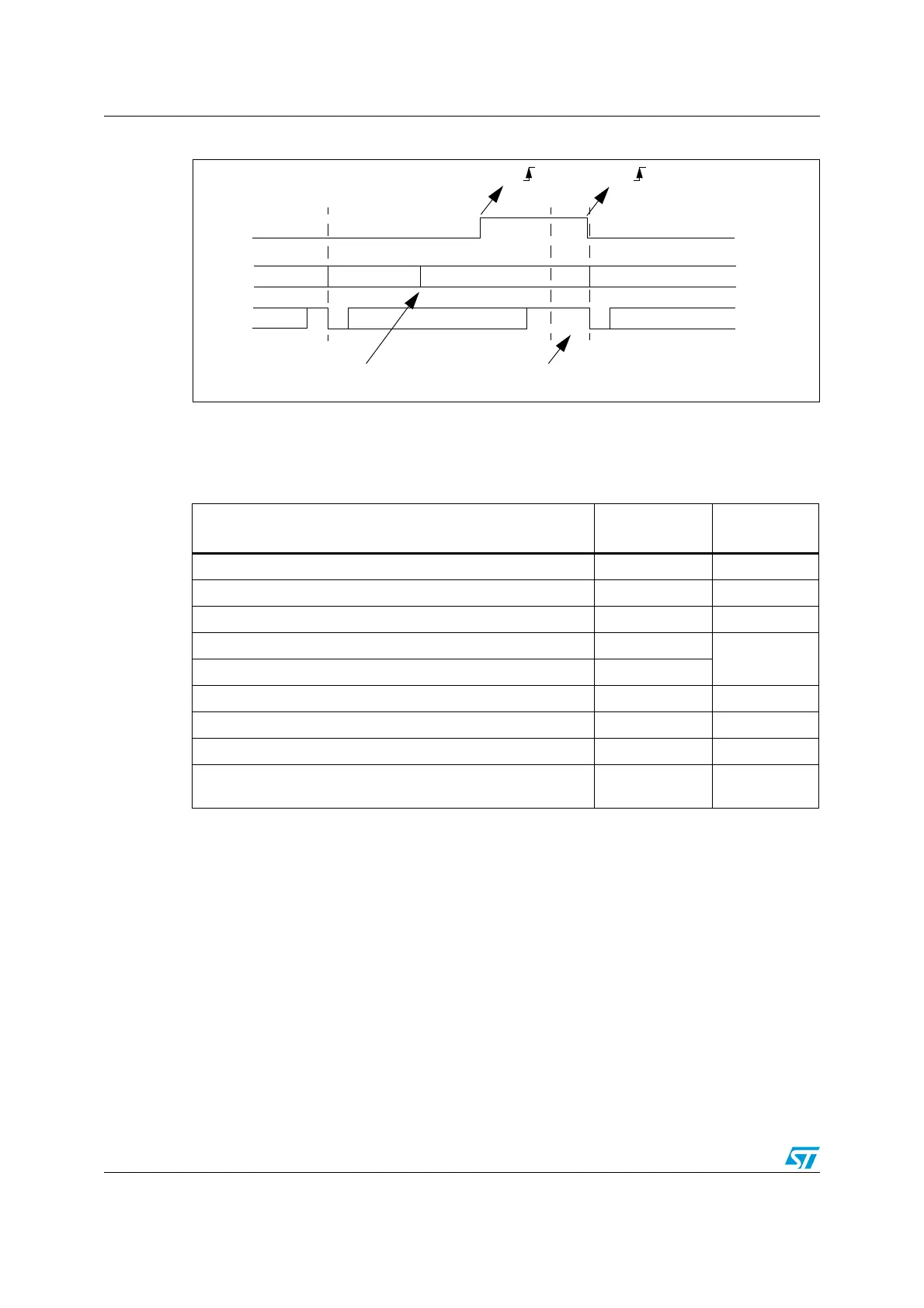

Figure 299. CTS flow control

27.4 USART interrupts

The USART interrupt events are connected to the same interrupt vector (see Figure 300).

● During transmission: Transmission Complete, Clear to Send or Transmit Data Register

empty interrupt.

● While receiving: Idle Line detection, Overrun error, Receive Data register not empty,

Parity error, LIN break detection, Noise Flag (only in multi buffer communication) and

Framing Error (only in multi buffer communication).

These events generate an interrupt if the corresponding Enable Control Bit is set.

Start

Bit

Stop

Bit

Data 2 Idle

Start

Bit

Data 3

TX

nCTS

CTS

Transmission of Data 3

Data 1

Stop

Bit

is delayed until nCTS = 0

CTS

Data 2 Data 3empty empty

Transmit data register

TDR

Writing data 3 in TDR

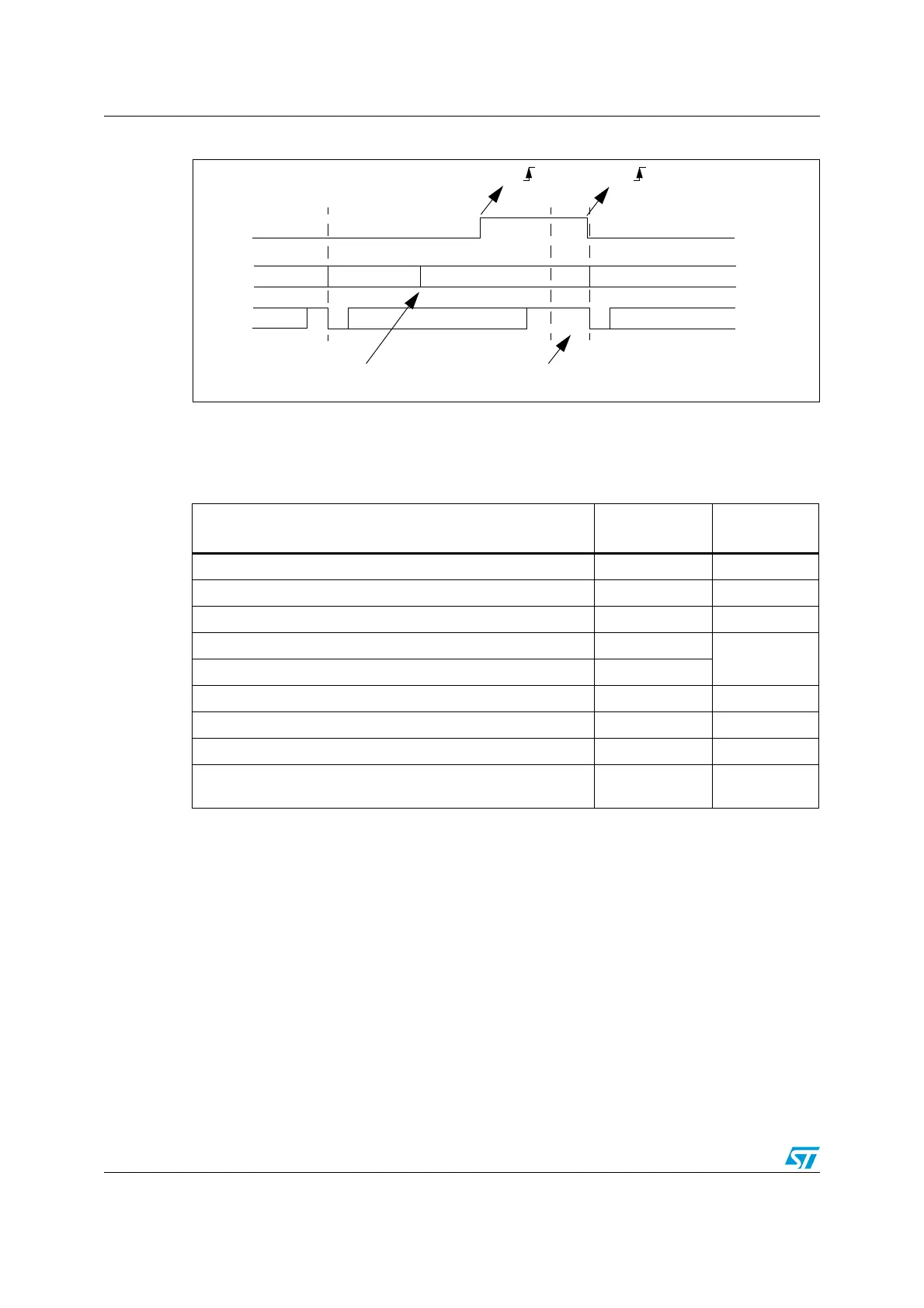

Table 195. USART interrupt requests

Interrupt event Event flag

Enable

Control bit

Transmit data register empty TXE TXEIE

CTS flag CTS CTSIE

Transmission complete TC TCIE

Received data ready to be read RXNE

RXNEIE

Overrun error detected ORE

Idle line detected IDLE IDLEIE

Parity error PE PEIE

Break flag LBD LBDIE

Noise flag, Overrun error and Framing error in multibuffer

communication

NE or ORE or FE EIE

(1)

1. This bit is used only when data reception is performed by DMA.

Loading...

Loading...