RM0008 General-purpose timers (TIM2 to TIM5)

Doc ID 13902 Rev 12 387/1096

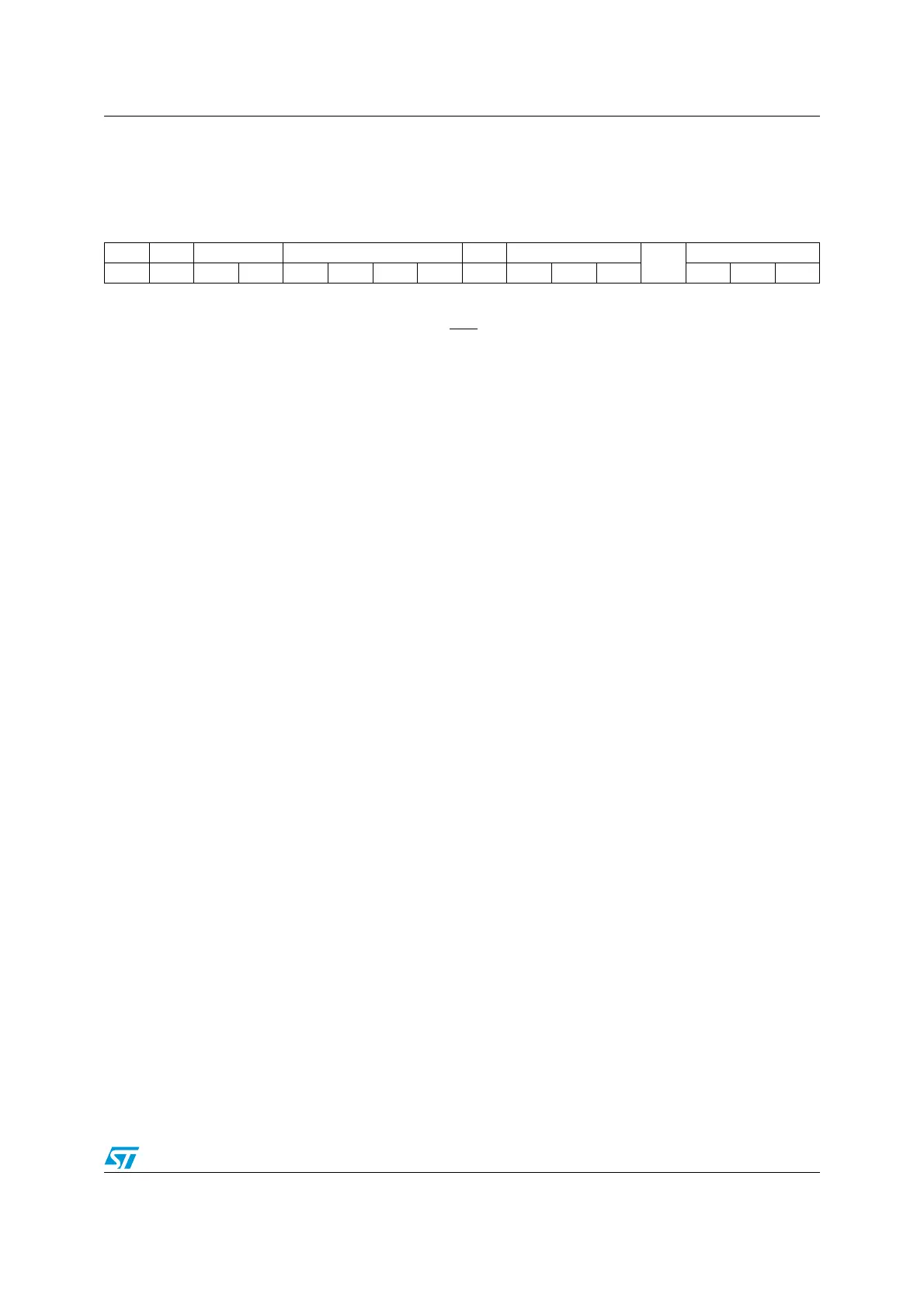

15.4.3 TIMx slave mode control register (TIMx_SMCR)

Address offset: 0x08

Reset value: 0x0000

1514131211109876543210

ETP ECE ETPS[1:0] ETF[3:0] MSM TS[2:0]

Res.

SMS[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 15 ETP: External trigger polarity

This bit selects whether ETR or ETR is used for trigger operations

0: ETR is non-inverted, active at high level or rising edge

1: ETR is inverted, active at low level or falling edge

Bit 14 ECE: External clock enable

This bit enables External clock mode 2.

0: External clock mode 2 disabled

1: External clock mode 2 enabled. The counter is clocked by any active edge on the ETRF

signal.

1: Setting the ECE bit has the same effect as selecting external clock mode 1 with TRGI

connected to ETRF (SMS=111 and TS=111).

2: It is possible to simultaneously use external clock mode 2 with the following slave modes:

reset mode, gated mode and trigger mode. Nevertheless, TRGI must not be connected to

ETRF in this case (TS bits must not be 111).

3: If external clock mode 1 and external clock mode 2 are enabled at the same time, the

external clock input is ETRF.

Bits 13:12 ETPS: External trigger prescaler

External trigger signal ETRP frequency must be at most 1/4 of CK_INT frequency. A

prescaler can be enabled to reduce ETRP frequency. It is useful when inputting fast external

clocks.

00: Prescaler OFF

01: ETRP frequency divided by 2

10: ETRP frequency divided by 4

11: ETRP frequency divided by 8

Bits 11:8 ETF[3:0]: External trigger filter

This bit-field then defines the frequency used to sample ETRP signal and the length of the

digital filter applied to ETRP. The digital filter is made of an event counter in which N events

are needed to validate a transition on the output:

0000: No filter, sampling is done at f

DTS

0001: f

SAMPLING

=f

CK_INT

, N=2

0010: f

SAMPLING

=f

CK_INT

, N=4

0011: f

SAMPLING

=f

CK_INT

, N=8

0100: f

SAMPLING

=f

DTS

/2, N=6

0101: f

SAMPLING

=f

DTS

/2, N=8

0110: f

SAMPLING

=f

DTS

/4, N=6

0111: f

SAMPLING

=f

DTS

/4, N=8

1000: f

SAMPLING

=f

DTS

/8, N=6

1001: f

SAMPLING

=f

DTS

/8, N=8

1010: f

SAMPLING

=f

DTS

/16, N=5

1011: f

SAMPLING

=f

DTS

/16, N=6

1100: f

SAMPLING

=f

DTS

/16, N=8

1101: f

SAMPLING

=f

DTS

/32, N=5

1110: f

SAMPLING

=f

DTS

/32, N=6

1111: f

SAMPLING

=f

DTS

/32, N=8

Loading...

Loading...