RM0008 Interrupts and events

Doc ID 13902 Rev 12 197/1096

10.2 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of up to 20 edge detectors in connectivity line

devices, or 19 edge detectors in other devices for generating event/interrupt requests. Each

input line can be independently configured to select the type (pulse or pending) and the

corresponding trigger event (rising or falling or both). Each line can also masked

independently. A pending register maintains the status line of the interrupt requests

10.2.1 Main features

The EXTI controller main features are the following:

● Independent trigger and mask on each interrupt/event line

● Dedicated status bit for each interrupt line

● Generation of up to 20 software event/interrupt requests

● Detection of external signal with pulse width lower than APB2 clock period. Refer to the

electrical characteristics section of the datasheet for details on this parameter.

10.2.2 Block diagram

The block diagram is shown in Figure 20.

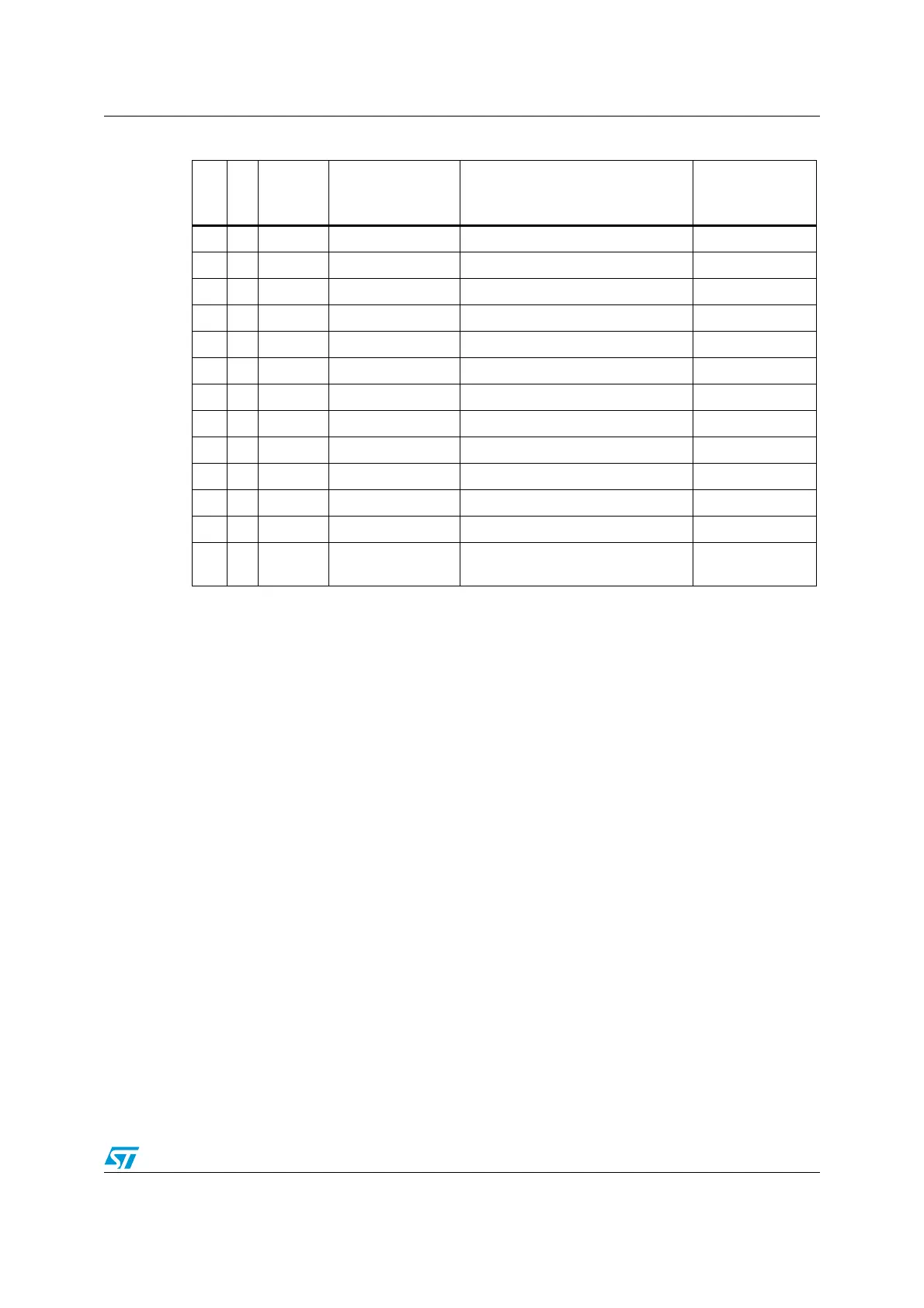

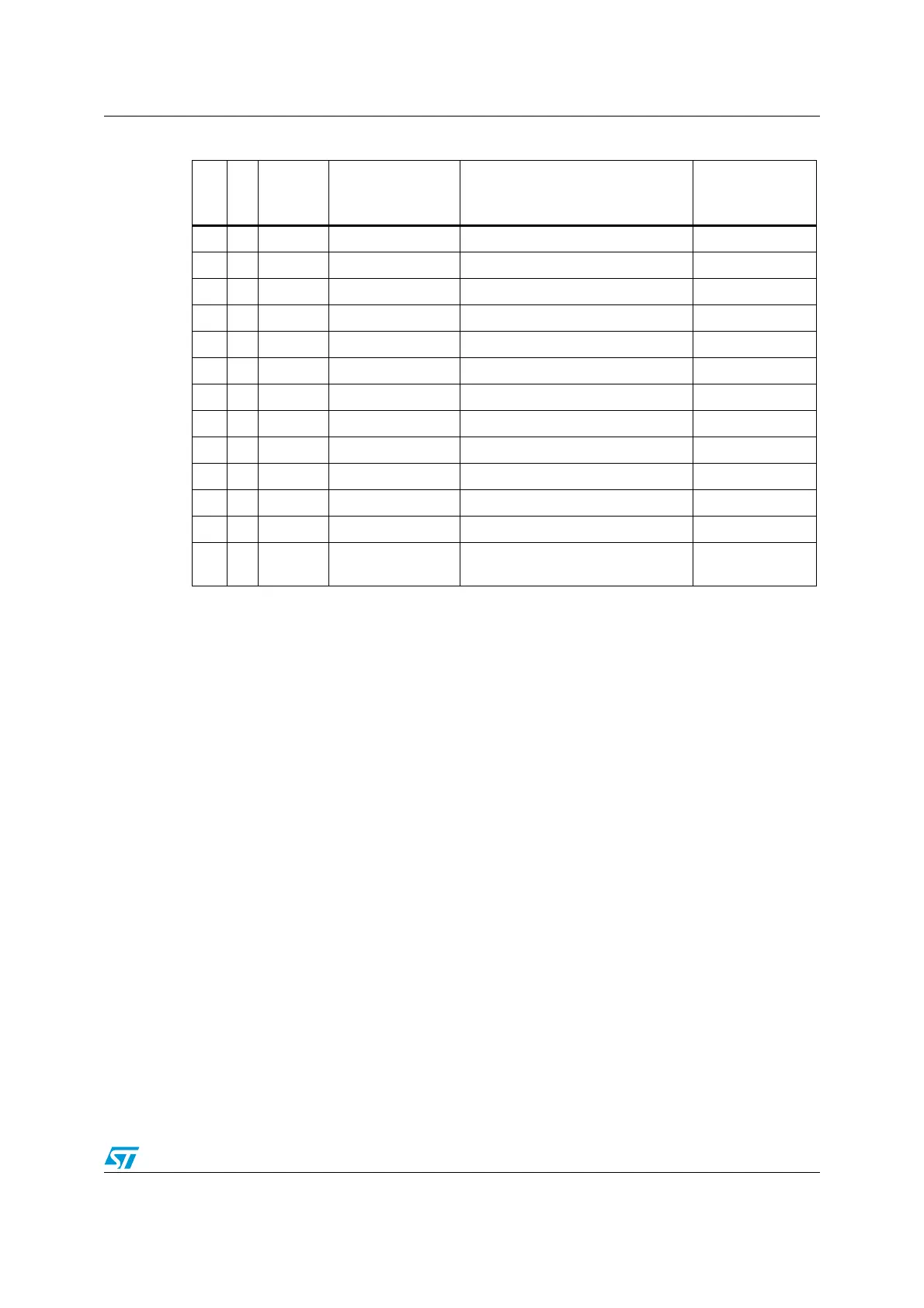

47 54 settable ADC3 ADC3 global interrupt 0x0000_00FC

48 55 settable FSMC FSMC global interrupt 0x0000_0100

49 56 settable SDIO SDIO global interrupt 0x0000_0104

50 57 settable TIM5 TIM5 global interrupt 0x0000_0108

51 58 settable SPI3 SPI3 global interrupt 0x0000_010C

52 59 settable UART4 UART4 global interrupt 0x0000_0110

53 60 settable UART5 UART5 global interrupt 0x0000_0114

54 61 settable TIM6 TIM6 global interrupt 0x0000_0118

55 62 settable TIM7 TIM7 global interrupt 0x0000_011C

56 63 settable DMA2_Channel1 DMA2 Channel1 global interrupt 0x0000_0120

57 64 settable DMA2_Channel2 DMA2 Channel2 global interrupt 0x0000_0124

58 65 settable DMA2_Channel3 DMA2 Channel3 global interrupt 0x0000_0128

59 66 settable DMA2_Channel4_5

DMA2 Channel4 and DMA2

Channel5 global interrupts

0x0000_012C

Table 63. Vector table for other STM32F10xxx devices (continued)

Position

Priority

Type of

priority

Acronym Description Address

Loading...

Loading...